# High-Performance Atomic-Layer-Deposited Indium Oxide 3-D Transistors and Integrated Circuits for Monolithic 3-D Integration

Mengwei Si<sup>©</sup>, Zehao Lin<sup>®</sup>, Zhizhong Chen, and Peide D. Ye<sup>®</sup>, Fellow, IEEE

Abstract—In this work, we report the experimental demonstration of In<sub>2</sub>O<sub>3</sub> 3-D transistors coated on fin structures and integrated circuits by a back-end-of-line (BEOL) compatible atomic layer deposition (ALD) process. High-performance planar back-gate In<sub>2</sub>O<sub>3</sub> transistors with high mobility of 113 cm<sup>2</sup>/V s and high maximum drain current ( $I_D$ ) of 2.5 mA/ $\mu$ m are achieved by channel thickness engineering and postdeposition annealing. The highperformance ALD In<sub>2</sub>O<sub>3</sub>-based zero-V<sub>GS</sub>-load inverter is demonstrated with a maximum voltage gain of 38 V/V and a minimum supply voltage ( $V_{\rm DD}$ ) down to 0.5 V. Top-gate indium oxide (In2O3) transistors by low-temperature ALD of both gate insulator and channel semiconductor are also demonstrated with  $I_D$  of 570  $\mu$ A/ $\mu$ m and low subthreshold slope (SS) down to 84.6 mV/decade. ALD In2O3 3-D Fin transistors with the top-gate structure are then demonstrated, benefiting from the conformal deposition capability of ALD. These results suggest that ALD oxide semiconductors and devices have unique advantages and are promising toward BEOL-compatible monolithic 3-D integration for 3-D integrated circuits.

Index Terms—3-D structure, atomic layer deposition (ALD), back-end-of-line (BEOL) compatible, indium oxide, oxide semiconductor, thin-film transistor.

## I. INTRODUCTION

XIDE semiconductors are the leading semiconducting channel materials for flat-panel display applications [1], [2]. Recently, indium oxide  $(In_2O_3)$  or doped- $In_2O_3$ , such

Manuscript received July 20, 2021; revised August 12, 2021; accepted August 15, 2021. Date of publication August 25, 2021; date of current version December 1, 2021. This work was supported in part by the Semiconductor Research Corporation (SRC) through the nanoelectronic COmputing REsearch (nCORE) Innovative Materials and Processes for Accelerated Compute Technologies (IMPACT) Center and in part by the SRC/Defense Advanced Research Projects Agency (DARPA) Joint University Microelectronics Program (JUMP) Applications and Systems Driven Center for Energy-Efficient Integrated NanoTechnologies (ASCENT) Center. The review of this article was arranged by Editor S. Yu. (Corresponding author: Peide D. Ye.)

Mengwei Si was with the School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907 USA, and also with the Birck Nanotechnology Center, Purdue University, West Lafayette, IN 47907 USA. He is now with the Department of Electronic Engineering, Shanghai Jiao Tong University, Shanghai 200240, China.

Zehao Lin, Zhizhong Chen, and Peide D. Ye are with the School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907 USA, and also with the Birck Nanotechnology Center, Purdue University, West Lafayette, IN 47907 USA (e-mail: yep@purdue.edu).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2021.3106282.

Digital Object Identifier 10.1109/TED.2021.3106282

as (indium gallium zinc oxide, IGZO), are being investigated as promising channel materials for back-end-of-line (BEOL) compatible transistors for monolithic 3-D integration [3], by both sputtering [4]–[13] and atomic layer deposition (ALD) [14]-[18], due to their high mobility, wide bandgap, low variability, and high stability. ALD-based oxide semiconductors [19]-[23] are of special interest due to the atomically smooth surface, ultrathin thickness, and the capability of conformal deposition on 3-D structures. Recently, high-performance back-gate ALD In<sub>2</sub>O<sub>3</sub> transistors have been demonstrated with a high drain current over 2 mA/ $\mu$ m in both depletion-mode (D-mode) and enhancement-mode (E-mode) operations [15], [16]. The devices have ultrascaled channel thickness  $(T_{ch})$  down to 0.7 nm, channel length down  $(L_{ch})$ to 40 nm, low thermal budget below 400 °C, and stability in the H<sub>2</sub> environment, which are highly compatible with the BEOL process. Meanwhile, for many practical applications, a top-gate device structure is required for integrated circuits and other applications. However, how to form high-quality gate dielectric on top of ALD In<sub>2</sub>O<sub>3</sub> and how to realize highperformance top-gate ALD In<sub>2</sub>O<sub>3</sub> transistors remain unclear.

In this work, the performance of back-gate ALD In<sub>2</sub>O<sub>3</sub> transistors is further enhanced by T<sub>ch</sub> engineering and postdeposition annealing. An optimized  $T_{ch}$  is determined to be 2.2–2.5 nm, achieving record high mobility of 113 cm $^2$ /V·s and record-high maximum drain current of 2.5 mA/ $\mu$ m at  $L_{\rm ch}$  of 40 nm and  $V_{\rm DS}=0.7$  V. The high-performance back-gate ALD In<sub>2</sub>O<sub>3</sub> transistors-based zero-V<sub>GS</sub>-load inverter is demonstrated with a maximum voltage gain of 38 V/V and a minimum supply voltage  $(V_{\rm DD})$  down to 0.5 V. Top-gate In<sub>2</sub>O<sub>3</sub> transistors are also demonstrated by low-temperature ALD of both gate insulator and channel semiconductor. High-performance top-gate In<sub>2</sub>O<sub>3</sub> transistors are realized with a maximum drain current ( $I_D$ ) of 570  $\mu$ A/ $\mu$ m and a low subthreshold slope (SS) down to 84.6 mV/decade. It is found that the deposition of hafnium oxide (HfO<sub>2</sub>) as gate insulator at low temperature and postdeposition annealing in O<sub>2</sub> at low temperature are critical to annihilate defects that are generated during the formation of top dielectrics and top-gate electrodes. ALD In<sub>2</sub>O<sub>3</sub> 3-D Fin transistors with top-gate structures coated on SiO<sub>2</sub> fin structures are also demonstrated for the first time, taking advantage of conformal deposition of ALD on 3-D structures.

0018-9383 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

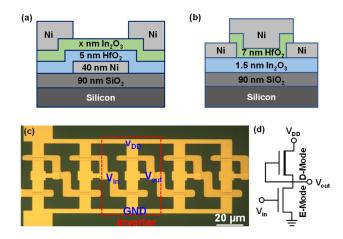

Fig. 1. Schematic of a planar  $In_2O_3$  transistor with (a) back-gate and (b) top-gate structures. (c) Photograph image of an  $In_2O_3$  zero- $V_{GS}$ -load inverter in a five-stage ring oscillator. (d) Circuit diagram of a zero- $V_{GS}$ -load inverter.

### II. EXPERIMENTS

Fig. 1 presents the schematic of planar (a) back-gate and (b) top-gate In<sub>2</sub>O<sub>3</sub> transistors. The back-gate device structure is similar to previously reported in [15] and [16], which is used for circuit demonstration. The gate-stack consists of 40-nm Ni as gate metal, 5-nm HfO<sub>2</sub> as gate dielectric, 0.5–3.5-nm In<sub>2</sub>O<sub>3</sub> as semiconducting channels, and 80-nm Ni as source/drain electrodes. The device fabrication process is similar to [15] and [16]. The fabricated devices were annealed in  $O_2$ ,  $N_2$ , or forming gas (FG, 96% N<sub>2</sub>/4% H<sub>2</sub>) for 30 s at different temperatures from 250 °C to 350 °C according to the optimized annealing conditions achieved in [15]. Fig. 1(c) shows the photograph of a fabricated In<sub>2</sub>O<sub>3</sub> zero-V<sub>GS</sub>-load inverter in a five-stage ring oscillator. The circuit diagram of the In<sub>2</sub>O<sub>3</sub> zero- $V_{GS}$ -load inverter is shown in Fig. 1(d). D-mode and E-mode transistors could be achieved by threshold voltage  $(V_{\rm T})$  engineering, such as plasma treatment described in [17]. The E-mode device has a channel length ( $L_{ch}$ ) of 2  $\mu$ m, while  $L_{\rm ch}$  of D-mode devices ( $L_{\rm D}$ ) varies from 0.1 to 0.3  $\mu m$  to engineer the load resistance.

The gate-stack of planar top-gate In<sub>2</sub>O<sub>3</sub> transistors, as shown in Fig. 1(b), includes 40-nm Ni as gate metal, 7-nm HfO<sub>2</sub> as gate dielectric, 1.5-nm In<sub>2</sub>O<sub>3</sub> as the semiconducting channel, and 40-nm Ni as source/drain electrodes. The device fabrication starts with a standard cleaning of 90-nm SiO<sub>2</sub>/p+ Si substrates. The 1.5-nm-thick In<sub>2</sub>O<sub>3</sub> films were then deposited by ALD at 225 °C, using (CH<sub>3</sub>)<sub>3</sub>In (TMIn) and H<sub>2</sub>O as In and O precursors. Channel isolation was done by wet etching use concentrated HCl. The 40-nm Ni was then deposited by e-beam evaporation as S/D contacts. Then, HfO<sub>2</sub> was deposited by ALD at various temperatures of 120 °C/150 °C/200 °C, using [(CH<sub>3</sub>)<sub>2</sub>N]<sub>4</sub>Hf (TDMAHf) and H<sub>2</sub>O as Hf and O precursors. The impact of ALD deposition temperature is discussed in great detail in the following section. The fabricated devices were annealed by rapid thermal annealing (RTA) in O<sub>2</sub> at different temperatures. 3-D Fin transistors with top-gate structures were fabricated on a SiO<sub>2</sub>/Si substrate with SiO2 fin structures. The top-gate dielectric of

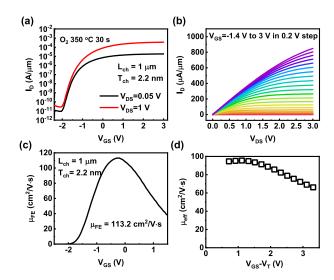

Fig. 2. (a)  $I_{\rm D}-V_{\rm GS}$  and (b)  $I_{\rm D}-V_{\rm DS}$  characteristics of a planar back-gate  $I_{\rm n2}O_3$  transistor with  $L_{\rm ch}$  of 1  $\mu$ m and  $T_{\rm ch}$  of 2.2 nm with  $O_2$  annealing at 350 °C for 30 s. (c)  $\mu_{\rm FE}$  versus  $V_{\rm GS}$  extracted from the maximum  $g_{\rm m}$  at  $V_{\rm DS}$  of 0.05 V from the transfer curve. (d)  $\mu_{\rm eff}$  versus  $V_{\rm GS}$  extracted from the  $g_{\rm d}$  from the output curve.

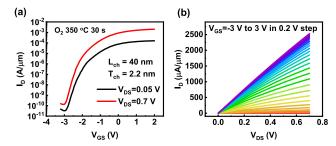

Fig. 3. (a)  $I_{\rm D}-V_{\rm GS}$  and (b)  $I_{\rm D}-V_{\rm DS}$  characteristics of a planar back-gate  $I_{\rm n_2}O_3$  transistor with  $L_{\rm ch}$  of 40 nm and  $T_{\rm ch}$  of 2.2 nm with  $O_2$  annealing at 350 °C.

7-nm HfO<sub>2</sub> was formed by low-temperature ALD at 120 °C, which is critical to form top-gate devices.

## III. RESULTS AND DISCUSSION

Fig. 2(a) shows the  $I_D$ – $V_{GS}$  characteristics of a planar  $In_2O_3$ transistor with  $L_{ch}$  of 1  $\mu$ m and  $T_{ch}$  of 2.2 nm with  $O_2$ annealing at 350 °C for 30 s. Fig. 2(b) shows the corresponding  $I_D$ – $V_{DS}$  characteristics of the same device, exhibiting high maximum  $I_D$  of 850  $\mu$ A/ $\mu$ m even with  $L_{ch}$  of 1  $\mu$ m and well-behaved drain current saturation at high  $V_{DS}$ . Such high  $I_D$  is the result of high field-effect mobility ( $\mu_{FE}$ ) of 113 cm<sup>2</sup>/V·s, as shown in Fig. 2(c), extracted from the maximum transconductance  $(g_m)$  at  $V_{DS}$  of 0.05 V. Effective mobility ( $\mu_{\rm eff}$ ) versus  $V_{\rm GS}$  extracted from drain conductance  $(g_d)$  are presented in Fig. 2(d), which is consistent with  $\mu_{FE}$ . Fig. 3(a) and (b) presents the  $I_D-V_{GS}$  and  $I_D-V_{DS}$  characteristics of an  $In_2O_3$  transistor with  $L_{ch}$  of 40 nm and  $T_{ch}$ of 2.2 nm, exhibiting a high maximum  $I_D$  of 2.5 mA/ $\mu$ m under  $V_{\rm DS} = 0.7 \text{ V}$  and  $V_{\rm GS} - V_{\rm T} = 4 \text{ V}$  with optimized  $T_{\rm ch}$ and annealing conditions. Further dielectric scaling is needed to realize  $V_{\rm GS} - V_{\rm T}$  approaching  $V_{\rm DS}$ .

The mobility of In<sub>2</sub>O<sub>3</sub> in this work is significantly improved compared to other ALD-based oxide

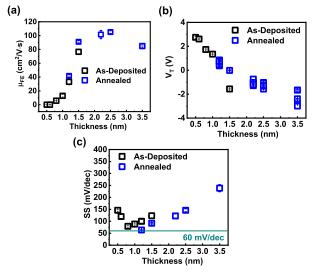

Fig. 4. (a)  $\mu_{\rm FE}$ , (b)  $V_{\rm T}$ , and (c) SS versus  $T_{\rm ch}$  extracted from as-deposited devices and devices with optimized annealing conditions.

semiconductors [19]-[23]. Such high mobility is achieved by  $T_{\rm ch}$  engineering and postdeposition annealing, as shown in Fig. 4(a). Average  $\mu_{FE} > 100 \text{ cm}^2/\text{V} \cdot \text{s}$  is achieved with  $T_{\rm ch}$  of 2.2–2.5 nm at optimized annealing conditions.  $\mu_{\rm FE}$ decreases rapidly with  $T_{\rm ch}$  below 1 nm, most likely due to the enhanced surface scattering and quantum confinement effect on the band structure [14].  $\mu_{\rm FE}$  decreases at  $T_{\rm ch}$ above 3 nm due to the higher carrier concentration and weaker gate electrostatic control, as also shown in  $V_{\rm T}$ versus  $T_{\rm ch}$  in Fig. 4(b). Postdeposition annealing for the reduction of oxygen vacancies in as-deposited films is needed to tune  $V_{\rm T}$  of devices with  $T_{\rm ch}$  above 2 nm to obtain a sufficiently high on/off ratio.  $V_{\rm T}$  of devices with certain  $T_{\rm ch}$  can be controlled by annealing conditions, as shown in Fig. 4(b). Fig. 4(c) shows  $T_{ch}$ -dependent SS extracted from as-deposited devices and devices with optimized annealing conditions, exhibiting SS close to the thermal limit of 60 mV/decade at room temperature at  $T_{\rm ch} \sim 1$  nm. The thickness-dependent SS indicates that the interface trap density  $D_{it}$  in the subthreshold region may be related to  $T_{ch}$ . However, the atomic configuration at the oxide/semiconductor interface does not have a  $T_{\rm ch}$  dependence. Thus, the defect energy levels should not change with respect to the vacuum level. Therefore, the only possible reason is that the band structure of  $In_2O_3$  is changing with  $T_{ch}$  (such as  $T_{ch}$ -dependent conduction band minimum,  $E_{\rm C}$ ) so that the Fermi level ( $E_{\rm F}$ ) alignment at the subthreshold region is changing. This result is consistent with previous theoretical analysis and density function theory (DFT) simulations [14].

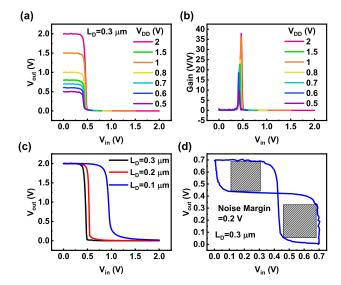

Fig. 5(a) presents  $V_{\rm out}$  versus  $V_{\rm in}$  curve of an  $\rm In_2O_3$  zero- $V_{\rm GS}$ -load inverter with  $L_{\rm D}$  of 0.3  $\mu{\rm m}$  at different  $V_{\rm DD}$ 's from 2 down to 0.5 V, showing well-behaved voltage transfer characteristics. The voltage gains are given in Fig. 5(b), achieving a maximum voltage gain of 38 V/V at  $V_{\rm DD}$  of 2 V. The midpoint voltage of the  $\rm In_2O_3$  zero- $V_{\rm GS}$ -load inverter can be engineered by tuning the load resistance and varying the channel length of the D-mode transistor, as illustrated in Fig. 5(c), providing the essential approach for  $V_{\rm DD}$  and midpoint voltage

Fig. 5. (a)  $V_{\rm out}$  versus  $V_{\rm in}$  and (b) voltage gain of an In<sub>2</sub>O<sub>3</sub> zero- $V_{\rm GS}$ -load inverter with  $L_{\rm D}$  of 0.3  $\mu$ m at different  $V_{\rm DD}$ 's. (c)  $V_{\rm out}$  versus  $V_{\rm in}$  of In<sub>2</sub>O<sub>3</sub> zero- $V_{\rm GS}$ -load inverters with different  $L_{\rm D}$ 's at  $V_{\rm DD}$  of 2 V. (d) NM of the In<sub>2</sub>O<sub>3</sub> zero- $V_{\rm GS}$ -load inverter as in (a) at  $V_{\rm DD}$  of 0.7 V.

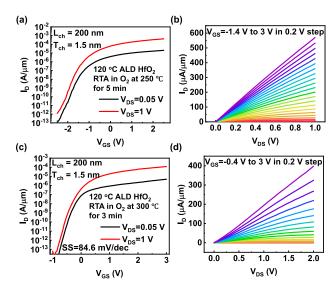

Fig. 6. (a)  $I_{\rm D}-V_{\rm GS}$  and (b)  $I_{\rm D}-V_{\rm DS}$  characteristics of a top-gate  $\ln_2{\rm O_3}$  transistor with  $L_{\rm ch}$  of 200 nm,  $T_{\rm ch}$  of 1.5 nm, 7-nm HfO<sub>2</sub> by ALD at 120 °C, and with RTA in O<sub>2</sub> at 250 °C for 5 min. (c)  $I_{\rm D}-V_{\rm GS}$  and (d)  $I_{\rm D}-V_{\rm DS}$  characteristics of a top-gate  $\ln_2{\rm O_3}$  transistor with  $L_{\rm ch}$  of 200 nm,  $T_{\rm ch}$  of 1.5 nm, 7-nm HfO<sub>2</sub> by ALD at 120 °C, and with RTA in O<sub>2</sub> at 300 °C for 3 min

engineering accordingly. Therefore, a sufficiently large noise margin (NM) can be achieved at a low  $V_{\rm DD}$  of 0.7 V, as shown in Fig. 5(d).

Fig. 6(a) and (b) shows the  $I_{\rm D}-V_{\rm GS}$  and  $I_{\rm D}-V_{\rm DS}$  characteristics of a top-gate  $\rm In_2O_3$  transistor with  $L_{\rm ch}$  of 200 nm and  $T_{\rm ch}$  of 1.5 nm. The HfO<sub>2</sub> gate dielectric in this device was deposited at 120 °C, and the device was annealed by RTA in O<sub>2</sub> at 250 °C for 5 min. The device exhibits well-behaved switching on and off characteristics, with a maximum  $I_{\rm D}$  of 570  $\mu A/\mu m$ . Fig. 6(c) and (d) shows the  $I_{\rm D}-V_{\rm GS}$  and  $I_{\rm D}-V_{\rm DS}$  characteristics of a top-gate  $\rm In_2O_3$  transistor with  $L_{\rm ch}$  of 200 nm,  $T_{\rm ch}$  of 1.5 nm, and with HfO<sub>2</sub> gate dielectric deposited at 120 °C and annealed by RTA in O<sub>2</sub> at 300 °C

Fig. 7. (a)  $I_D$ – $V_{GS}$  characteristics at  $V_{DS}$  of 1 V of top-gate  $In_2O_3$  transistors with different annealing conditions.  $I_D$ – $V_{GS}$  at  $V_{DS}$  of 1 V of top-gate  $In_2O_3$  transistors with different annealing conditions with HfO<sub>2</sub> gate oxide deposited by ALD at 120 °C, (b) 150 °C, and (c) 200 °C.

for 3 min. This device has a maximum  $I_D$  of 397  $\mu A/\mu m$ and SS of 84.6 mV/decade. The small SS at the subthreshold region indicates a high-quality oxide/semiconductor interface. The interface trap density  $D_{it}$  at the sub-threshold region is estimated to be  $\sim 5-6 \times 10^{12}$ /cm<sup>2</sup> eV.  $D_{\rm it}$  at the HfO<sub>2</sub>/In<sub>2</sub>O<sub>3</sub> interface in a top-gate device is much larger than that in a back-gate device. The main difficulty for the integration of top-gate on the ALD In<sub>2</sub>O<sub>3</sub> channel is from the ALD HfO<sub>2</sub> process. Hf-O bond with dissociation energy of 801 kJ/mol is much more stable compared to the In-O bond of 346 kJ/mol. ALD of HfO<sub>2</sub> on In<sub>2</sub>O<sub>3</sub> generates more O vacancies in In<sub>2</sub>O<sub>3</sub> and induces much more charge density. Meanwhile, it also degrades In<sub>2</sub>O<sub>3</sub> film and HfO<sub>2</sub>/In<sub>2</sub>O<sub>3</sub> interface quality. Appropriate O<sub>2</sub> annealing can fill these O vacancies and heal most of the defects from the process so that SS of top-gate devices can be improved. To further improve the oxide/semiconductor interface quality, a top gate oxide or interfacial layer with low bond dissociate energy is preferred, and a lower interface trap density may be achieved. For example, Al-O has dissociation energy of 512 kJ/mol, and Mg-O has dissociation energy of 394 kJ/mol.

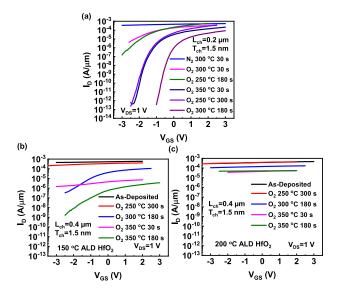

Fig. 7(a) shows the transfer characteristics at  $V_{\rm DS}$  of 1 V of top-gate In<sub>2</sub>O<sub>3</sub> transistors with different annealing conditions where the ALD HfO<sub>2</sub> was grown at 120 °C. As-fabricated devices, without annealing or devices annealed in the N<sub>2</sub> environment, cannot be turned off, the reason why these devices cannot be turned off is not just due to the high carrier density because the drain current density here is smaller than previous reported values in devices with similar dimensions [15]. Thus, the poor switching characteristics are also partly due to the high trap density at the HfO<sub>2</sub>/In<sub>2</sub>O<sub>3</sub> interface, which is generated during the ALD HfO<sub>2</sub> process. Devices annealed in O<sub>2</sub> show well-behaved switching on/off characteristics, suggesting that O<sub>2</sub> is necessary to heal these defects, also indicating that these defects are likely to be O deficiencies.

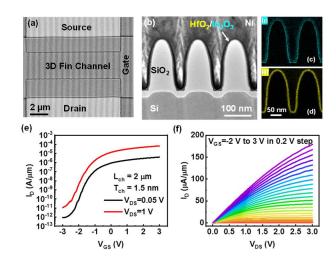

Fig. 8. (a) SEM image of an  $\ln_2 O_3$  3-D Fin transistor with top-gate structure. SiO<sub>2</sub> fin structures were fabricated by SEMATECH. (b) TEM image of a new type of 3-D Fin transistor with top-gate structure and  $\ln_2 O_3$  channel. EDX mapping under HAADF STEM of (c) In and (d) Hf, showing the conformal coating around the fin structure by ALD. (e)  $I_D - V_{GS}$  and (f)  $I_D - V_{DS}$  characteristics of an  $\ln_2 O_3$  3-D Fin transistor with  $L_{ch}$  of 2  $\mu$ m and  $T_{ch}$  of 1.5 nm.

Therefore, from the above experimental observation, it is speculated that the deposition of  $HfO_2$  by ALD generates defects at the  $HfO_2/In_2O_3$  interface, most likely because the pulse of Hf precursor (TDMAHf) takes oxygen atoms away from  $In_2O_3$ , leading to the formation of oxygen vacancies at  $HfO_2/In_2O_3$  interface. Such defects can only be healed in an  $O_2$  environment by  $O_2$  annealing. Such a process also depends on the annealing time, as shown in Fig. 7(a). It is also found that devices with  $O_2$  annealing at 250 °C have higher  $I_D$  than devices with  $O_2$  annealing at 300 °C with a similar threshold voltage ( $V_T$ ). Therefore, low-temperature  $O_2$  annealing is preferred to maintain high mobility.

Fig. 7 presents the  $I_D$ – $V_{GS}$  characteristics at  $V_{DS}$  of 1 V of top-gate In<sub>2</sub>O<sub>3</sub> transistors with O<sub>2</sub> annealing and with HfO<sub>2</sub> gate oxide deposited by ALD at (a) 120 °C, (b) 150 °C, and (c) 200 °C. As we can see, the on/off ratio of the devices degrades significantly with higher temperature HfO<sub>2</sub> ALD process and indicates that much more defects are generated at higher ALD temperature most likely due to the stronger reaction between TDMAHf and In<sub>2</sub>O<sub>3</sub>. All these detailed experiments offer a consistent picture of the challenge of integration of ALD HfO<sub>2</sub> on top of In<sub>2</sub>O<sub>3</sub>.

Fig. 8(a) shows the scanning electron microscopic (SEM) image of an  $In_2O_3$  3-D Fin transistor with top-gate structure, capturing the gate metal, source/drain contacts, and the fin structures. Fig. 8(b)–(d) presents the transmission electron microscope (TEM) image and energy-dispersive X-ray spectroscopic (EDX) mapping under high-angle annular dark-field imaging (HAADF) scanning transmission electron microscope (STEM) of an  $In_2O_3$  3-D fin transistor. ALD  $In_2O_3$  channel with  $T_{\rm ch}$  of 1.5 nm is conformally coated on top of SiO<sub>2</sub> fin structures with a fin height of 180 nm and a fin pitch of 130 nm, as shown in the EDX element mapping of Hf and In. Fig. 8(e) shows  $I_D$ – $V_{GS}$  characteristics of an  $In_2O_3$  3-D Fin transistor with  $L_{\rm ch}$  of 2  $\mu$ m and  $T_{\rm ch}$  of 1.5 nm, exhibiting well-behaved transfer characteristics. Fig. 8(f) shows the

corresponding  $I_{\rm D}$ – $V_{\rm DS}$  characteristics with a maximum  $I_{\rm D}$  of 180  $\mu$ A/ $\mu$ m, normalized by device width, which is about two times larger than that from its top-gate planar counterpart. The 3-D fin structure provides an effective approach to increase the drive current without increasing the device area. The ultrathin channel thickness and the top-gate non-self-align structure with a large link resistance make  $I_{\rm D}$  smaller than those from back-gate planar devices.

### IV. CONCLUSION

In summary, high-performance 3-D Fin transistors and integrated circuits based on BEOL compatible oxide semiconductors by ALD are demonstrated. High mobility of 113 cm<sup>2</sup>/V · s and high maximum drain current of 2.5 mA/ $\mu$ m are achieved. The demonstration of 3-D devices and integrated circuits suggests that ALD oxide semiconductors and devices have their unique advantages over sputtering films and are promising toward BEOL-compatible monolithic 3-D integration for 3-D integrated circuits.

# REFERENCES

- K. Nomura, A. Takagi, T. Kamiya, H. Ohta, M. Hirano, and H. Hosono, "Amorphous oxide semiconductors for high-performance flexible thinfilm transistors," *Jpn. J. Appl. Phys.*, vol. 45, no. 5, pp. 4303–4308, Apr. 2006, doi: 10.1143/JJAP.45.4303.

- [2] T. Kamiya and H. Hosono, "Material characteristics and applications of transparent amorphous oxide semiconductors," NPG Asia Mater., vol. 2, no. 1, pp. 15–22, Jan. 2010, doi: 10.1038/asiamat.2010.5.

- [3] S. Datta, S. Dutta, B. Grisafe, J. Smith, S. Srinivasa, and H. Ye, "Back-end-of-line compatible transistors for monolithic 3-D integration," *IEEE Micro*, vol. 39, no. 6, pp. 8–15, Nov. 2019, doi: 10.1109/ MM.2019.2942978.

- [4] S. Li et al., "Nanometre-thin indium tin oxide for advanced high-performance electronics," *Nature Mater.*, vol. 18, no. 10, pp. 1091–1097, Oct. 2019, doi: 10.1038/s41563-019-0455-8.

- [5] S. Samanta, K. Han, C. Sun, C. Wang, A. V.-Y. Thean, and X. Gong, "Amorphous IGZO TFTs featuring extremely-scaled channel thickness and 38 nm channel length: Achieving record high Gm,<sub>max</sub> of 125 μS/μm at V<sub>DS</sub> of 1 V and I<sub>ON</sub> of 350 μm," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2020, doi: 10.1109/VLSITechnology18217.2020.9265052.

- [6] W. Chakraborty, B. Grisafe, H. Ye, I. Lightcap, K. Ni, and S. Datta, "BEOL compatible dual-gate ultra thin-body W-doped indium-oxide transistor with I<sub>on</sub> = 370μA/μm, SS = 73 mV/dec and I<sub>on</sub> /I<sub>off</sub> ratio > 4×109," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2020, doi: 10.1109/VLSITechnology18217.2020.9265064.

- [7] S. Li, C. Gu, X. Li, R. Huang, and Y. Wu, "10-nm channel length indium-tin-oxide transistors with  $I_{on}=1860~\mu\text{A}/\mu\text{m}$ ,  $G_m=1050~\mu\text{S}/\mu\text{m}$  at  $V_{ds}=1~V$  with BEOL compatibility," in *IEDM Tech. Dig.*, Dec. 2020, pp. 905–908, doi: 10.1109/IEDM13553.2020.9371966.

- [8] J. Wu, F. Mo, T. Saraya, T. Hiramoto, and M. Kobayashi, "A monolithic 3D integration of RRAM array with oxide semiconductor FET for in-memory computing in quantized neural network AI applications," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2020, pp. 1–2, doi: 10.1109/VLSITechnology18217.2020.9265062.

- [9] S. Dutta et al., "Monolithic 3D integration of high endurance multi-bit ferroelectric FET for accelerating compute-in-memory," in *IEDM Tech. Dig.*, Dec. 2020, pp. 801–804, doi: 10.1109/IEDM13553.2020.9371974.

- [10] H. Fujiwara, Y. Sato, N. Saito, T. Ueda, and K. Ikeda, "Surrounding gate vertical-channel FET with a gate length of 40 nm using BEOL-compatible high-thermal-tolerance In-Al-Zn oxide channel," *IEEE Trans. Electron Devices*, vol. 67, no. 12, pp. 5329–5335, Dec. 2020, doi: 10.1109/TED.2020.3021996.

- [11] M. Si et al., "Indium-tin-oxide transistors with one nanometer thick channel and ferroelectric gating," ACS Nano, vol. 14, no. 9, pp. 11542–11547, Sep. 2020, doi: 10.1021/acsnano.0c03978.

- [12] K. Han et al., "First demonstration of oxide semiconductor nanowire transistors: A novel digital etch technique, IGZO channel, nanowire width down to 20 nm, and I<sub>on</sub> exceeding 1300 μA/μm," in Proc. IEEE Symp. VLSI Technol., Jun. 2021, pp. 1–2.

- [13] M. Si et al., "BEOL compatible indium-tin-oxide transistors: Switching of ultrahigh-density 2-D electron gas over 0.8 × 1014/cm<sup>2</sup> at oxide/oxide interface by the change of ferroelectric polarization," *IEEE Trans. Electron Devices*, vol. 68, no. 7, pp. 3195–3199, Jul. 2021, doi: 10.1109/TED.2021.3061038.

- [14] M. Si et al., "Why In<sub>2</sub>O<sub>3</sub> can make 0.7 nm atomic layer thin transistors," *Nano Lett.*, vol. 21, no. 1, pp. 500–506, Jan. 2021, doi: 10.1021/acs.nanolett.0c03967.

- [15] M. Si, A. Charnas, Z. Lin, and P. D. Ye, "Enhancement-mode atomic-layer-deposited In<sub>2</sub>O<sub>3</sub> transistors with maximum drain current of 2.2 A/mm at drain voltage of 0.7 V by low-temperature annealing and stability in hydrogen environment," *IEEE Trans. Electron Devices*, vol. 68, no. 3, pp. 1075–1080, Mar. 2021, doi: 10.1109/TED.2021.3053229.

- [16] M. Si, Z. Lin, A. Charnas, and P. D. Ye, "Scaled atomic-layer-deposited indium oxide nanometer transistors with maximum drain current exceeding 2 A/mm at drain voltage of 0.7 V," *IEEE Electron Device Lett.*, vol. 42, no. 2, pp. 184–187, Feb. 2021, doi: 10.1109/LED.2020. 3043430.

- [17] A. Charnas, M. Si, Z. Lin, and P. D. Ye, "Enhancement-mode atomic-layer thin In<sub>2</sub>O<sub>3</sub> transistors with maximum current exceeding 2 A/mm at drain voltage of 0.7 V enabled by oxygen plasma treatment," *Appl. Phys. Lett.*, vol. 118, no. 5, Feb. 2021, Art. no. 052107, doi: 10.1063/5.0039783.

- [18] M. Si, Z. Lin, Z. Chen, and P. D. Ye, "First demonstration of atomic-layer-deposited BEOL-compatible In<sub>2</sub>O<sub>3</sub> 3D fin transistors and integrated circuits: High mobility of 113 cm<sup>2</sup>/V·s, maximum drain current of 2.5 mA/μM and maximum voltage gain of 38 V/V in In<sub>2</sub>O<sub>3</sub> inverter," in *Proc. IEEE Symp. VLSI Technol.*, vol. 2021, p. T2-4.

- [19] D. A. Mourey, D. A. Zhao, J. Sun, and T. N. Jackson, "Fast PEALD ZnO thin-film transistor circuits," *IEEE Trans. Electron Devices*, vol. 57, no. 2, pp. 530–534, Feb. 2010, doi: 10.1109/TED.2009.2037178.

- [20] H. Y. Kim et al., "Low-temperature growth of indium oxide thin film by plasma-enhanced atomic layer deposition using liquid dimethyl(Nethoxy-2,2-dimethylpropanamido)indium for high-mobility thin film transistor application," ACS Appl. Mater. Interface, vol. 8, no. 40, pp. 26924–26931, Oct. 2016, doi: 10.1021/acsami.6b07332.

- [21] Q. Ma et al., "Atomic-layer-deposition of indium oxide nano-films for thin-film transistors," Nanosc. Res. Lett., vol. 13, no. 1, pp. 1–8, Dec. 2018, doi: 10.1186/s11671-017-2414-0.

- [22] J. Lee et al., "High mobility ultra-thin crystalline indium oxide thin film transistor using atomic layer deposition," Appl. Phys. Lett., vol. 113, no. 11, Sep. 2018, Art. no. 112102, doi: 10.1063/1.5041029.

- [23] J. Sheng et al., "Amorphous IGZO TFT with high mobility of ~70 cm²/(V s) via vertical dimension control using PEALD," ACS Appl. Mater. Interface, vol. 11, no. 43, pp. 40300–40309, Oct. 2019, doi: 10.1021/acsami.9b14310.