# Quantitative Characterization of Ferroelectric/Dielectric Interface Traps by Pulse Measurements

Junkang Li<sup>®</sup>, *Student Member, IEEE*, Mengwei Si<sup>®</sup>, Yiming Qu<sup>®</sup>, *Student Member, IEEE*, Xiao Lyu, and Peide D. Ye<sup>®</sup>, *Fellow, IEEE*

Abstract—The ferroelectric (FE) polarization switching behavior in the HfZrO<sub>2</sub> (HZO) FE/dielectric (FE/DE) stack is investigated systematically by charge responses from pulse measurements. The trapped charge density at the FE/DE interface related with the FE polarization switching is found to be 1.2  $\times$  10<sup>14</sup> cm<sup>-2</sup> according to the leakage-current-assist polarization switching mechanism. Furthermore, by the time-dependent nonswitching charge responses, the extra FE/DE interface trap density of 1.1 imes $10^{13}$  cm<sup>-2</sup> is confirmed, which is not related but can be detected along with the FE polarization switching. The quantitative characterization reveals the huge amount of FE/DE interface traps and their dominant role in the FE operation of HZO FE/DE stack, which improves the proposed leakagecurrent-assist polarization switching model. This improved model provides a more comprehensive understanding of the polarization switching in the HZO FE/DE stack and new insights on HZO negative-capacitance (NC) and FE fieldeffect transistors (FETs).

Index Terms—Charge response, ferroelectric (FE) polarization switching, FE/dielectric (FE/DE), leakage-currentassist polarization switching mechanism, trapped charges.

## I. INTRODUCTION

THE ever-rising quest for data storage over the past several years has expedited the development of new emerging memory technology, such as the nonvolatile ferroelectric (FE)

Manuscript received December 12, 2020; accepted January 18, 2021. Date of publication February 2, 2021; date of current version February 24, 2021. This work was supported in part by the Applications and Systems-Driven Center for Energy-Efficient Integrated Nano Technologies (ASCENT), one of six centers in the Joint University Microelectronics Program (JUMP), a Semiconductor Research Corporation (SRC) Program sponsored by the Defense Advanced Research Projects Agency (DARPA) and in part by the Air Force Office of Scientific Research. The work of Junkang Li and Yiming Qu was supported by the Chinese Scholarship Council. The review of this article was arranged by Editor T. Grasser. (*Corresponding author: Peide D. Ye.*)

Junkang Li and Yiming Qu are with the Birck Nanotechnology Center, School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907 USA, and also with the College of Electronic Engineering and Information Science, Zhejiang University, Hangzhou 310027, China.

Mengwei Si, Xiao Lyu, and Peide D. Ye are with the Birck Nanotechnology Center, School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907 USA (e-mail: yep@purdue.edu).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2021.3053497.

Digital Object Identifier 10.1109/TED.2021.3053497

device [1]–[3]. FE hafnium oxide, such as hafnium zirconium oxide ( $Hf_{0.5}Zr_{0.5}O_2$ , HZO), has been recently discovered to be a CMOS compatible FE insulator [4]-[6]. The HZO-based FE-gated field-effect transistors (FETs), as one of the most promising candidates for memory devices, have attracted considerable interest with many desirable features, including high integration density, low power consumption, fast access speed, and nondestructive read-out operation [7]-[12]. The FE/dielectric (FE/DE) stack is critical to understand the device operation of FE-FETs, since the DE layer is inevitable as part of gate-stack to passivate the substrate surface. The FE/DE stack is fundamentally different from an FE capacitor and a DE capacitor in series, since some interfacial coupling effects are involved [13]-[15]. Charge trapping and detrapping at the FE/DE interface are considered as the dominant interfacial coupling effects in the FE/DE stack, which has been demonstrated by the previously proposed leakage-currentassist polarization switching mechanism [15]-[21]. The FE/DE interface traps are found to have a dramatic impact on the performance and reliability of FE-gated FETs, including memory window (MW), retention characteristic, endurance behavior, and imprint voltage [18]-[20], [23], [24]. Therefore, some techniques to quantitatively characterize the FE/DE interface traps were proposed, showing the consistent trapped charge density of  $\sim 10^{14}$  cm<sup>-2</sup> [20]–[22]. This experimental result indicates that the polarization switching of FE/DE stack is almost dominated by charging and discharge of FE/DE interface traps. On the other hand, negative capacitance (NC) FET, which is developed recently by applying the quasistatic NC (QSNC) concept, presents a different perspective [25]–[30]. In the definition of QSNC, the DE layer between the semiconductor channel and the FE insulator is required to provide the capacitance matching and stabilize the hysteresisfree NC effect. Capacitance boost and charge enhancement have been observed in the HZO/Al<sub>2</sub>O<sub>3</sub> stack by fast pulse measurement, suggesting the NC effect without FE polarization switching [31]–[34]. These phenomena from FE-FET and NC-FET in the FE-gated FETs are quite different and both are strongly related to the charge accumulation in the FE/DE stack or at the FE/DE interface. Therefore, the comprehensive understanding of the charge behavior through the FE/DE stack, especially at the FE/DE interface, and its impact on the FE

0018-9383 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

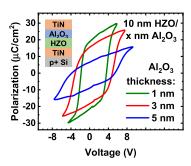

Fig. 1. P-V hysteresis loops of the 10 nm HZO/1, 3, 5 nm Al<sub>2</sub>O<sub>3</sub> stacks. The inset is the structure of these stacks.

polarization switching is critical to study the nature of FE-FET and NC-FET operations.

In this work, HZO and Al<sub>2</sub>O<sub>3</sub> are chosen as the FE and DE insulators to study the FE polarization switching in the HZO FE/DE stack, respectively. The charge behaviors with the evolutions of time and voltage are revealed in the HZO/Al<sub>2</sub>O<sub>3</sub> stack by using the pulse measurement [32]-[34]. Three different waveform schemes are applied to monitor the transient charging and discharging processes through the FE/DE stack during FE operation. Leakage-current-assist polarization switching mechanism is quantitatively demonstrated while the NC effect induced charge enhancement is not observed. By considering the leakage-current-assist polarization switching in the FE/DE stack, the trapped charge density at the FE/DE interface related with the FE polarization switching can be extracted. In addition, traps at the FE/DE interface unrelated but along with the FE polarization switching process is characterized by the nonswitching charge responses, further suggesting the importance of FE/DE interface in the FE/DE stack. The quantitative charge characterization explains the charge trapping effect at the FE/DE interface during the FE and non-FE operations of HZO/Al<sub>2</sub>O<sub>3</sub> stack reasonably, which improves the proposed leakage-current-assist FE polarization switching model.

### **II. EXPERIMENTS**

The device fabrication process is similar to the previous report in [15]. The 30 nm bottom TiN electrode was first deposited on the SiO<sub>2</sub> substrate by atomic layer deposition (ALD) at 250 °C, using tetrakis (dimethylamino) titanium (TDMAT) ([(CH<sub>3</sub>)<sub>2</sub>N]<sub>4</sub>Ti) and NH<sub>3</sub> as the Ti and N precursors. Following that, a 10-nm ALD HZO (Hf:Zr = 1:1) film was deposited at 200 °C, using tetrakis (dimethylamino) hafnium (TDMAHf) ([(CH<sub>3</sub>)<sub>2</sub>N]<sub>4</sub>Hf), tetrakis (dimethylamino) zirconium (TDMAZr) ([(CH<sub>3</sub>)<sub>2</sub>N]<sub>4</sub>Zr), and H<sub>2</sub>O as the Hf, Zr, and O precursors. The stacked 1, 3, and 5 nm Al<sub>2</sub>O<sub>3</sub> layers were then deposited at 200 °C, using trimethylaluminium (TMA) (Al(CH<sub>3</sub>)<sub>3</sub>) and H<sub>2</sub>O as Al and O precursors. Afterward, a 30-nm TiN electrode was formed on the top of HZO/Al<sub>2</sub>O<sub>3</sub> stack, using the same process conditions as for the bottom electrode. Finally, the samples were annealed at 500  $^{\circ}$ C in an N<sub>2</sub> ambient for 1 min by rapid thermal annealing. The pure HZO capacitor without Al<sub>2</sub>O<sub>3</sub> was also fabricated as the control sample. The capacitor area used in this work is 5024  $\mu$ m<sup>2</sup> unless otherwise specified.

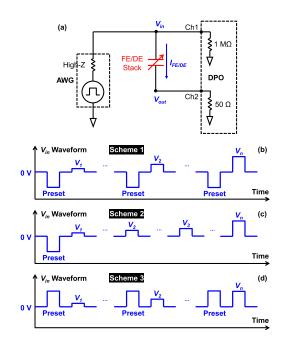

Fig. 2. (a) Circuit diagram of the pulse measurement setup. (b) First  $V_{in}$  waveform scheme with negative preset at the beginning of each voltage pulse to trace the consecutive charge behavior during FE polarization switching. (c) Second  $V_{in}$  waveform scheme with negative preset only before a single FE polarization switching process to study the transient charge variation during FE polarization switching. (d) Third  $V_{in}$  waveform scheme with positive preset at the beginning of each voltage pulse to characterize the charge trapping unrelated with the FE polarization switching.

#### III. RESULTS AND DISCUSSION

Fig. 1 shows the typical polarization–voltage (P-V) hysteresis loops of the HZO/Al<sub>2</sub>O<sub>3</sub> stacks with the HZO of 10 nm and the Al<sub>2</sub>O<sub>3</sub> of 1, 3, and 5 nm. The significant decrease of remnant polarization  $(P_r)$  in P-V hysteresis loops is observed with a thicker DE layer, illustrating their profound ferroelectricity and the previously reported leakage-current-assist polarization switching mechanism. The insect shows the structure of these HZO/Al<sub>2</sub>O<sub>3</sub> stacks. Fig. 2(a) shows the circuit diagram of the pulse measurement setup. An Agilent 33220A artificial waveform generator (AWG) and a TDS500B series digital phosphor oscilloscope (DPO) were used for real-time monitoring of charge behavior in the 10 nm HZO/3 nm Al<sub>2</sub>O<sub>3</sub> stack. The input voltage pulses  $(V_{in})$  with different amplitude, rise time, and pulsewidth were applied by AWG and detected by one channel of the DPO with the input resistance of 1 M $\Omega$ . Simultaneously, the output voltages  $(V_{out})$  were also measured by another channel of the DPO with the input resistance of 50  $\Omega$ . Therefore, the current through the HZO/Al<sub>2</sub>O<sub>3</sub> stack during operation can be obtained by  $I_{\text{FE/DE}} = V_{\text{out}}/50 \Omega$ , and the voltage drop across the HZO/Al<sub>2</sub>O<sub>3</sub> stack,  $V_{FE/DE}$ , is equal to  $V_{\rm in}-V_{\rm out}$ . Finally, the charge density ( $\sigma$ ) with the evolution of time (t) at one voltage level is expressed as

$$\sigma = \int_{-\infty}^{t} (I_{\text{FE/DE}} - I_0). \tag{1}$$

Here,  $I_0$  is the deviation current at  $V_{in} = 0$  V due to the nonideal voltage offset in the real measurement system. Fig. 2(b)-(d) gives three different waveform schemes. The first  $V_{in}$  waveform scheme, as shown in Fig. 2(b), applies a series of input pulses with the fixed rise time and pulsewidth and the incrementally increasing voltage amplitude. After each pulse, the resulting charging and discharging processes are recorded. At the beginning of each input pulse, the HZO/Al<sub>2</sub>O<sub>3</sub> stack is reset to the initial negative polarization state. It is to obtain the consecutive charge density during FE polarization switching and to compare with the charge accumulation in a pure Al<sub>2</sub>O<sub>3</sub> capacitor at the same Al<sub>2</sub>O<sub>3</sub> thickness. To analyze the charge behavior in detail, the second  $V_{in}$  waveform scheme is designed as shown in Fig. 2(c). It applies one poling pulse at the beginning and then a series of input pulses. It is assumed that the integration of the incremental charge densities for *n* voltage pulses is nearly the same as the charge density obtained after the nth pulse in the first scheme. Thus, all the charge densities taken from n voltage pulses should reveal the evolution of charge behavior during a single FE polarization switching process, allowing the dynamics of FE polarization switching to be traced and studied. Furthermore, the charge trapping and detrapping unrelated with FE polarization switching can be characterized by changing the negative preset voltages in the first waveform scheme to be positive, as the third  $V_{in}$  waveform scheme shown in Fig. 2(d). The positive preset pulses at the beginning of each input pulse ensure the HZO/Al<sub>2</sub>O<sub>3</sub> stack works in the nonswitching mode. The discrepancy of charge density at different rise time can be observed and explained by the time-dependent trap responses in the non-FE operation of the FE/DE stack. Fig. 3 gives an example of the pulse waveforms and the resulting charge densities in the 10 nm HZO/3 nm Al<sub>2</sub>O<sub>3</sub> stack by using the first  $V_{in}$  waveform scheme. Fig. 3(a) shows the typical Vin waveforms with the rise time of 100 ns, the pulsewidth of 500 ns, and the voltage amplitude from 0.5 to 8 V (preset voltage is -8 V and not shown here). The calculated  $V_{\text{FE/DE}}$ and  $I_{\text{FE/DE}}$  as a function of time are presented in Fig. 3(b) and (c), respectively. Fig. 3(d) shows the integrated charge density from Fig. 3(c). From the charge transients in Fig. 3(d), three important charge densities are extracted for each voltage pulse: the total injected charge density into the HZO/Al<sub>2</sub>O<sub>3</sub> stack during the charging process,  $\sigma_{max}$ ; the residual charge density in the HZO/Al<sub>2</sub>O<sub>3</sub> stack after the applied voltage returns to zero again,  $\sigma_{res}$ ; and the difference between  $\sigma_{max}$ and  $\sigma_{\rm res}$  in the discharging process, which is expressed as  $\sigma_{\rm rev}$  that can be reversibly stored and released from the HZO/Al<sub>2</sub>O<sub>3</sub> stack. The  $\sigma_{rev}$  is critical to investigate the NC effect induced charge enhancement and capacitance boost [33]. All three charge densities— $\sigma_{max}$ ,  $\sigma_{res}$ , and  $\sigma_{rev}$ —are shown in Fig. 3(e) as a function of the voltage across the  $HZO/Al_2O_3$ stack,  $V_{\text{max}}$ , where  $V_{\text{max}}$  is the applied maximum  $V_{\text{FE/DE}}$ . The  $\sigma_{\rm res}$  is observed to increase distinctly when  $V_{\rm max}$  is larger than 5 V, which induces a lower reversible charge during the discharging process. In addition, to examine the influence of leakage current through the HZO/Al<sub>2</sub>O<sub>3</sub> stack on the pulse measurement, the I-V property of the HZO/Al<sub>2</sub>O<sub>3</sub> stack is also measured, as shown in Fig. 3(f). The leakage current of  $\sim 3 \times 10^{-3}$  A/cm<sup>2</sup> at 8 V is confirmed to be negligible in the extraction of charge densities, especially for  $\sigma_{res}$ , which will be illustrated in detail later. It means that the increase of  $\sigma_{\rm res}$

Fig. 3. (a) Input voltage pulses ( $V_{in}$ ), (b) voltage drops over the HZO/Al<sub>2</sub>O<sub>3</sub> stack ( $V_{FE/DE}$ ), (c) measured current response ( $I_{FE/DE}$ ), and (d) integrated charge, respectively, as a function of time. (e) Total injected charge density,  $\sigma_{max}$ , and residual charge density,  $\sigma_{res}$ , together with their difference,  $\sigma_{rev} = \sigma_{max} - \sigma_{res}$ . These are derived from (d) as a function *f* the voltage across the HZO/Al<sub>2</sub>O<sub>3</sub> stack ( $V_{max}$ ) in (b). (f) *I*-*V* property of the HZO/Al<sub>2</sub>O<sub>3</sub> stack to examine the influence of leakage current on the pulse measurement.

is dominated by polarization switching rather than the charge accumulation from the leakage current. However, the leakage current will increase exponentially if the HZO/Al<sub>2</sub>O<sub>3</sub> stack is biased toward the breakdown voltage continuously, which can no longer be ignored in the extracted  $\sigma_{max}$  and  $\sigma_{res}$ .

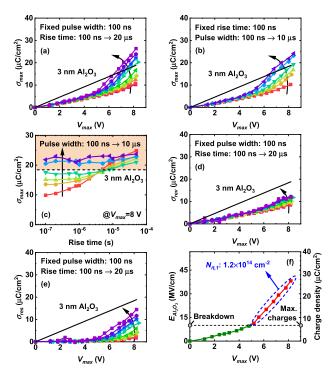

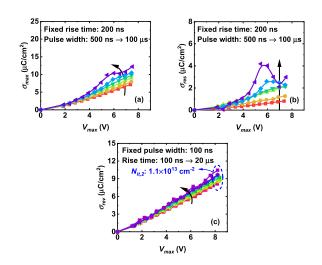

Fig. 4 shows the measurement results of consecutive  $\sigma_{max}$ ,  $\sigma_{\rm res}$ , and  $\sigma_{\rm rev}$  variations by using the first  $V_{\rm in}$  waveform scheme. By fixing the pulsewidth to 100 ns and changing the rise time from 100 ns to 20  $\mu$ s for the input pulses,  $\sigma_{max}$  as a function of  $V_{\text{max}}$  is obtained, as shown in Fig. 4(a). Similarly, this relationship with the fixed rise time of 100 ns and the different pulsewidth from 100 ns to 10  $\mu$ s is also presented in Fig. 4(b).  $\sigma_{\text{max}}$  is observed to be improved significantly after extending the rise time or the pulsewidth. For the  $\sigma_{max}$ - $V_{\rm max}$  curve with the pulsewidth of 100 ns and the rise time of 20  $\mu$ s in Fig. 4(a), up to a pulse height of about 5 V, the slope of the curve,  $dQ_{\text{max}}/dV_{\text{max}}$ , corresponding to the capacitance of the HZO/Al<sub>2</sub>O<sub>3</sub> stack in the charging process, is roughly constant while increasing obviously for greater pulse heights. These phenomena can be ascribed to the full FE polarization switching with the long enough pulse duration in the charging process. Simultaneously, the  $\sigma_{\rm max}-V_{\rm max}$  curve of a 3 nm  $Al_2O_3$  capacitor by the traditional C-V method is also plotted in Fig. 4(a) and (b) to compare the capability of charge storage in these two different systems. It shows the apparent charge enhancement and capacitance boost over the 3 nm

Fig. 4. (a) Consecutive  $\sigma_{max} - V_{max}$  relationships at different rise time and (b) different pulsewidth by the first  $V_{in}$  waveform scheme. (c) Summarized  $\sigma_{max}$  at  $V_{max} = 8$  V with the evolution of rise time at different pulsewidth. (d)  $\sigma_{rev}$  and (e)  $\sigma_{res}$  as a function of  $V_{max}$  at different rise time. (f) Calculated electric field across the Al<sub>2</sub>O<sub>3</sub> layer ( $E_{Al_2O_3}$ ) as a function of  $V_{max}$  to extract the trapped charge density at the FE/DE interface related with the FE polarization switching ( $N_{it,1}$ ).

Al<sub>2</sub>O<sub>3</sub> capacitor in the condition of sufficient FE polarization switching, achieved by the persistent pulse duration and large voltage amplitude. The  $\sigma_{\text{max}}$  at  $V_{\text{max}} = 8$  V for different rise times and pulsewidth are summarized in Fig. 4(c). The dashed line defines the density of charges accumulated in the 3 nm Al<sub>2</sub>O<sub>3</sub> capacitor at the same voltage. It is confirmed that charge enhancement can be realized when the pulsewidth lasts over 1  $\mu$ s or the rise time exceeds 5  $\mu$ s. The two values of pulsewidth and rise time are both larger than the extracted polarization switching time by the positive up negative down (PUND) measurement and the fitting with nucleation limited switching (NLS) model (data not shown here), indicating the relationship of charge enhancement and capacitance boost with the full FE polarization switching in the charging process [35], [36]. For the demonstration of this concept, the evolutions of  $\sigma_{rev}$  and  $\sigma_{res}$  with  $V_{max}$  at the fixed pulsewidth and different rise time during the discharging process are presented in Fig. 4(d) and (e), respectively. It is found in Fig. 4(d) that there is no charge enhancement for  $\sigma_{rev}$ even at the rise time of 20  $\mu$ s and the voltage amplitude of 8 V, because a large proportion of charges,  $\sigma_{res}$ , are remained in the HZO/Al<sub>2</sub>O<sub>3</sub> stack for FE polarization switching as shown in Fig. 4(e). It should be noted here that  $\sigma_{res}$  is immune to the influence of the leakage currents through the HZO/Al<sub>2</sub>O<sub>3</sub> stack as mentioned above, since the resulting charge densities by the integrations of these currents over various pulse durations are all ignorable to the corresponding  $\sigma_{\rm res}$ . Therefore, the NC effect-induced charge enhancement cannot be realized in the

FE/DE stack due to the FE polarization switching, even in the condition of short pulse. In addition, it can be seen in Fig. 4(d) that the slope of the  $\sigma_{\rm max}$ -V<sub>max</sub> curve (corresponding to the capacitance by the C-V measurement) for the HZO/Al<sub>2</sub>O<sub>3</sub> stack around  $V_{\text{max}} = 8$  V with the pulsewidth of 20  $\mu$ s is almost similar with that for the 3 nm Al<sub>2</sub>O<sub>3</sub> capacitor, which is larger than the capacitance of an FE capacitor and a DE capacitor in series. This capacitance boost for the HZO/Al<sub>2</sub>O<sub>3</sub> stack is also visible in the C-V measurement and might be contributed by the coexistence of stabilized NC and charge trapping in the FE/DE stack [15]. To further understand the charge behavior in the HZO/Al<sub>2</sub>O<sub>3</sub> stack, an ideal situation with the assumption of charge balance between the HZO and Al<sub>2</sub>O<sub>3</sub> layers and no extra charge trapping is considered. Then, the electric field across the Al<sub>2</sub>O<sub>3</sub> layer ( $E_{Al_2O_3}$ ) as a function of  $V_{\text{max}}$  during the charging process is calculated by the equation as

$$E_{\rm Al_2O_3} = Q_{\rm Al_2O_3}(V_{\rm max})/d_{\rm Al_2O_3}C_{\rm Al_2O_3}$$

(2)

where  $Q_{Al_2O_3}(V_{max})$  is the charge stored on the Al<sub>2</sub>O<sub>3</sub> layer at different  $V_{\text{max}}$  and assumed to be equal to the charge totally injected into the HZO/Al<sub>2</sub>O<sub>3</sub> stack ( $\sigma_{max}$ ), and  $d_{Al_2O_3}$  is the thickness of the Al<sub>2</sub>O<sub>3</sub> layer, and  $C_{Al_2O_3}$  is the capacitance of the Al<sub>2</sub>O<sub>3</sub> layer. Fig. 4(f) shows the calculated  $E_{Al_2O_3}$  and the corresponding  $\sigma_{\rm max}$  with the evolution of  $V_{\rm max}$ .  $E_{\rm Al_2O_3}$  is found to be up to  $\sim$ 40 MV/cm, which of course cannot happen. Typically, the Al<sub>2</sub>O<sub>3</sub> layer will break down and become leaky if the  $E_{Al_2O_3}$  exceeds 10 MV/cm, which happens immediately when  $V_{\text{max}}$  is over coercive voltage in this work. Thus, the charge density over the breakdown  $E_{Al_2O_3}$  should be supplied from the leakage current through the Al<sub>2</sub>O<sub>3</sub> layer, which is consistent with the proposed leakage-current-assist polarization switching mechanism [15]. By using this mechanism, the unbalanced charge density from the leakage current is calculated to be  $1.2 \times 10^{14}$  cm<sup>-2</sup>. This component is intended to balance the polarization charges on the HZO layer, which should be mainly located at the HZO/Al<sub>2</sub>O<sub>3</sub> interface but still slightly inside the Al<sub>2</sub>O<sub>3</sub> layer, and therefore defined as the charge density at the FE/DE interface related with the FE polarization switching  $(N_{it,1})$ . It should be noted that the initial charges at the FE/DE interface are not included in the result. This measured  $N_{it,1}$  agrees well with the reported data numerically [21], [22]. It means that the FE polarization charges are mainly balanced by the trapped charges at the FE/DE interface from the leakage current instead of the charges stored on the Al<sub>2</sub>O<sub>3</sub> layer. Here, the leakage current through the Al<sub>2</sub>O<sub>3</sub> layer to assist the FE polarization switching, which contributes to  $\sigma_{res}$ , is different from the negligible leakage component through the HZO/Al2O3 stack mentioned in Fig. 3(f). However, if the applied voltage is increased continuously before the breakdown, leakage current should be excluded from  $\sigma_{\text{max}}$  in the calculation of  $N_{\text{it},1}$  and  $N_{\text{it},1}$  will tend to be constant finally.

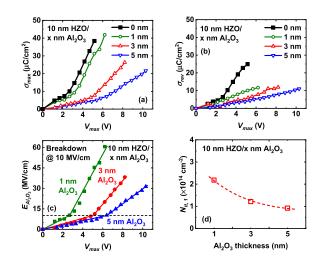

To justify the charge trapping at the FE/DE interface, the charge responses by the first  $V_{in}$  waveform scheme are investigated more comprehensively, including the pure HZO capacitor and the HZO/Al<sub>2</sub>O<sub>3</sub> stacks with different Al<sub>2</sub>O<sub>3</sub> thicknesses. Fig. 5(a) and (b) shows the consecutive

Fig. 5. Consecutive (a)  $\sigma_{max}$  and (b)  $\sigma_{res}$  as a function of  $V_{max}$  at different Al<sub>2</sub>O<sub>3</sub> thicknesses by the first  $V_{in}$  waveform scheme with the long enough pulse duration for full FE polarization switching. (c)  $E_{Al_2O_3} - V_{max}$  relationships with the assumption of no FE/DE interface traps at different Al<sub>2</sub>O<sub>3</sub> thicknesses. (d) Calculated  $N_{it,1}$  from (c) at different Al<sub>2</sub>O<sub>3</sub> thicknesses according to the leakage-current-assist polarization switching mechanism.

$\sigma_{\rm max}$ -V<sub>max</sub> and  $\sigma_{\rm rev}$ -V<sub>max</sub> dependence measured in the HZO and HZO/Al<sub>2</sub>O<sub>3</sub> stacks. Here, the pulse durations for the measurements to extract these charge densities are long enough to fully polarize the HZO and HZO/Al<sub>2</sub>O<sub>3</sub> stacks, where the rise time is 500 ns and the pulsewidth is 10  $\mu$ s. It can be observed that the  $\sigma_{\text{max}}$ -V<sub>max</sub> curves exhibit the similar changing trends with increasing  $V_{\text{max}}$ , which are all featured with rapid growths in charge densities at the specific voltage values due to the FE polarization switching. Regarding  $\sigma_{rev}$ , the pure HZO capacitor shows a different charge response. A steep slope increase of  $\sigma_{rev}$  is detected upon FE polarization switching. This is due to the direct contacts of HZO with two electrodes, which facilitates the total capture of responded polarization charges. However, in the HZO/Al<sub>2</sub>O<sub>3</sub> stack, the slow-growth of  $\sigma_{rev}$  can be ascribed to the screen effect of Al<sub>2</sub>O<sub>3</sub> layer and charge trapping at the FE/DE interface. Furthermore,  $E_{Al_2O_3}$ at different Al<sub>2</sub>O<sub>3</sub> thicknesses (1, 3, and 5 nm) are obtained from Fig. 5(a) by using the calculation method in Fig. 4(f), as shown in Fig. 5(c). It is obvious that the HZO/Al<sub>2</sub>O<sub>3</sub> stacks show an increase of voltage onset for breakdown, which can be used as a sanity check for the FE/DE interface traps. In addition, the steeper slopes of  $\sigma_{rev}-V_{max}$  curves after breakdown suggests two different physical mechanisms to charge responses across the DE layer, which should be the leakage currents after breakdown. From these leakage currents for the unbalanced charges trapped at the FE/DE interface, Nit,1 at different Al<sub>2</sub>O<sub>3</sub> thicknesses are calculated and summarized as shown in Fig. 5(d). Undoubtedly, a thicker  $Al_2O_3$  layer is found to be able to passivate the FE/DE interface better.

Fig. 6(a) and (b) shows the transient  $\sigma_{max}$  and  $\sigma_{res}$  variations of the 10 nm HZO/3 nm Al<sub>2</sub>O<sub>3</sub> stack during FE polarization switching by the second  $V_{in}$  waveform scheme, respectively. It is found that the transient  $\sigma_{max}$  has a sudden increase around the coercive voltage (~5 V) with enough pulse duration, which can be interpreted by the dramatic increase of  $\sigma_{res}$  for the full

Fig. 6. Transient (a)  $\sigma_{max}$  and (b)  $\sigma_{res}$  as a function of  $V_{max}$  at different rise time by the second  $V_{in}$  waveform scheme. (c) Rise time-dependent  $\sigma_{rev}$  as a function of  $V_{max}$  by the third  $V_{in}$  waveform scheme to obtain the FE/DE interface trap density unrelated with the FE polarization switching  $(N_{it,2})$ .

FE polarization switching. The relationships of transient  $\sigma_{max}$ - $V_{\rm max}$  and  $\sigma_{\rm res} - V_{\rm max}$  give a more detailed description of charge behavior during FE polarization switching. Fig. 6(c) shows the time-dependent  $\sigma_{rev}-V_{max}$  curves for the nonswitching operation by the third Vin waveform scheme. It is found that the capacitance of the HZO/Al<sub>2</sub>O<sub>3</sub> stack from the  $\sigma_{rev}$ - $V_{\rm max}$  relationship measured by the short pulse (the pulsewidth of 100 ns and the rise time of 100 ns),  $\sim 1 \ \mu$ F/cm<sup>2</sup>, is almost the same as the value of an FE capacitor (~2.3  $\mu$ F/cm<sup>2</sup>) and a DE capacitor (~1.9  $\mu$ F/cm<sup>2</sup>) in series. However, the discrepancy of  $\sigma_{rev}$  at different pulse durations (the rise time from 100 ns to 20  $\mu$ s) increases with a larger  $V_{\text{max}}$ . This phenomenon can be attributed to the charge trapping and detrapping unrelated with the FE polarization switching in the FE/DE stack, whose density is calculated to be  $1.1 \times 10^{13}$  $cm^{-2}$  within the time constant of 20  $\mu$ s. Here, the trapped charge density is normalized at the FE/DE interface due to the relatively poor film quality at the heterogeneous interface, which is therefore, defined as  $N_{it,2}$ . However, considering the issue of voltage-dependent  $N_{it,2}$ , it is quite different from  $N_{\rm it,1}$ , because  $\sigma_{\rm rev}$  is immune to leakage currents and  $N_{\rm it,2}$  is highly dependent on the band bending. The experiment result is consistent with the capacitance boost observed in Fig. 4(d)and interface characterization by conductance method [22].

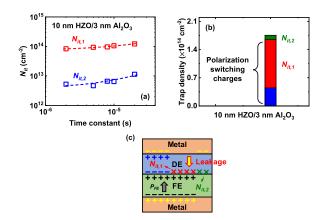

Fig. 7(a) shows the  $N_{it,1}$  and  $N_{it,2}$  distributions with time constant in the 10 nm HZO/3 nm Al<sub>2</sub>O<sub>3</sub> stack. Almost linear time-dependent charge trapping indicates the uniform energy distribution of FE/DE interface trap densities. However, due to the minimum pulse duration limitation to fully polarize the HZO/Al<sub>2</sub>O<sub>3</sub> stack, the available characterization range for trap levels is narrow by the pulse measurements. Fig. 7(b) summarizes these two kinds of FE/DE interface traps and compares them with the polarization switching charges from the 10 nm HZO/3 nm Al<sub>2</sub>O<sub>3</sub> stack. It is found that the charge trapping at the FE/DE interface ( $N_{it,1}$ ) dominates the FE polarization switching [in Fig. 2(b) or (c)] while extra FE/DE interface

Fig. 7. (a)  $N_{it,1}$  and  $N_{it,2}$  distributions with time constant in the 10 nm HZO/3 nm Al<sub>2</sub>O<sub>3</sub> stack. (b)  $N_{it,1}$  and  $N_{it,2}$  components of trapped charges generated during FE polarization switching for the 10 nm HZO/3 nm Al<sub>2</sub>O<sub>3</sub> stack. (c) Schematic of the improved leakage-current-assist FE polarization switching model for the FE/DE stack.

traps  $(N_{it,2})$  can be also detected even without FE polarization switching [in Fig. 2(d)]. The significance of FE/DE interface traps has to be considered in the understanding of HZO/Al<sub>2</sub>O<sub>3</sub> stack operation. The proposed  $N_{it,1}$  and  $N_{it,2}$  in this work are similar with the reported stable and unstable trapped charges, by definition, in [37], respectively. The  $N_{it,2}$  and unstable trapped charges both originate in the defects unrelated with the FE polarization switching and can be detrapped soon. Fig. 7(c)describes an improved leakage-current-assist FE polarization switching model for the FE/DE stack. During a full FE polarization switching of the FE layer, the charge density from the FE layer,  $P_{\text{FE}}$ , is equivalently induced in the DE layer. However, considering the maximum limitation of the charge storage capability, the DE layer will softly break down and become leaky. Most of  $P_{\rm FE}$  will be balanced by  $N_{\rm it,1}$  supplied from the leakage current through the DE layer to finish the FE polarization switching. For the non-FE component,  $N_{it,2}$ , charge trapping also occurs but at a lower amount level, which is still along with the FE operation process. This improved model indicates that, in the FETs based on the FE/DE gate-stack, the carrier density in the inversion channel is essentially not improved by the FE polarization switching effect due to the serious charge trapping in the FE/DE stack or at the FE/DE interface [21]. Due to the limitation of the FE material used in this work, the general schematic about FE polarization switching of the FE/DE stack might be restricted within the HZO FE system and can provide new insights in the understanding of the HZO FE-FET and NC-FET operations.

## **IV. CONCLUSION**

In summary, the charge behavior in the HZO FE/DE stack has been investigated systematically by pulse measurements. The trapped FE/DE interface charges during FE polarization switching are quantitatively characterized by using the leakage-current-assist polarization switching mechanism and the time-dependent nonswitching charge responses. The charge trapping effect at the FE/DE interface dominates the FE polarization switching of the HZO FE/DE stack significantly. The huge amount of FE/DE interface traps cannot be ignored to understand the device operations of the HZO FE-FETs and perhaps also NC-FETs. This work provides a guideline to study the device physics of FE-gated FETs.

#### REFERENCES

- S. L. Miller and P. J. McWhorter, "Physics of the ferroelectric nonvolatile memory field effect transistor," *J. Appl. Phys.*, vol. 72, no. 12, pp. 5999–6010, Dec. 1992, doi: 10.1063/1.351910.

- [2] S. Yin and O. Kaynak, "Big data for modern industry: Challenges and trends [point of view]," *Proc. IEEE*, vol. 103, no. 2, pp. 143–146, Feb. 2015, doi: 10.1109/JPROC.2015.2388958.

- [3] T. Mikolajick, U. Schroeder, and S. Slesazeck, "The past, the present, and the future of ferroelectric memories," *IEEE Trans. Electron Devices*, vol. 67, no. 4, pp. 1434–1443, Apr. 2020, doi: 10.1109/TED.2020.2976148.

- [4] J Müller *et al.*, "Ferroelectric Zr<sub>0.5</sub>Hf<sub>0.5</sub>O<sub>2</sub> thin films for nonvolatile memory applications," *Appl. Phys. Lett.*, vol. 99, no. 11, Sep. 2011, Art. no. 112901, doi: 10.1063/1.3636417.

- [5] J. Müller *et al.*, "Ferroelectricity in simple binary ZrO<sub>2</sub> and HfO<sub>2</sub>," *Nano Lett.*, vol. 12, no. 8, pp. 4318–4323, Aug. 2012, doi: 10.1021/nl302049k.

- [6] S. J. Kim, J. Mohan, S. R. Summerfelt, and J. Kim, "Ferroelectric Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> thin films: A review of recent advances," *JOM*, vol. 71, no. 1, pp. 246–255, Jan. 2019, doi: 10.1007/s11837-018-3140-5.

- [7] A. Q. Jiang, H. J. Lee, C. S. Hwang, and J. F. Scott, "Sub-picosecond processes of ferroelectric domain switching from field and temperature experiments," *Adv. Funct. Mater.*, vol. 22, no. 1, pp. 192–199, Jan. 2012, doi: 10.1002/adfm.201101521.

- [8] H. Mulaosmanovic *et al.*, "Evidence of single domain switching in hafnium oxide based FeFETs: Enabler for multi-level FeFET memory cells," in *IEDM Tech. Dig.*, Dec. 2015, pp. 688–690, doi: 10.1109/IEDM.2015.7409777.

- [9] M. Trentzsch et al., "A 28 nm HKMG super low power embedded NVM technology based on ferroelectric FETs," in *IEDM Tech. Dig.*, Dec. 2016, pp. 294–297, doi: 10.1109/IEDM.2016.7838397.

- [10] K. Chatterjee *et al.*, "Self-aligned, gate last, FDSOI, ferroelectric gate memory device with 5.5-nm Hf<sub>0.8</sub>Zr<sub>0.2</sub>O<sub>2</sub>, high endurance and breakdown recovery," *IEEE Electron Device Lett.*, vol. 38, no. 10, pp. 1379–1382, Oct. 2017, doi: 10.1109/LED.2017.2748992.

- [11] W. Chung, M. Si, P. R. Shrestha, J. P. Campbell, K. P. Cheung, and P. D. Ye, "First direct experimental studies of Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> ferroelectric polarization switching down to 100-picosecond in sub-60 mV/dec germanium ferroelectric nanowire FETs," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2018, pp. 89–90, doi: 10.1109/VLSIT.2018.8510652.

- [12] X. Lyu, M. Si, P. R. Shrestha, K. P. Cheung, and P. D. Ye, "First direct measurement of sub-nanosecond polarization switching in ferroelectric hafnium zirconium oxide," in *IEDM Tech. Dig.*, Dec. 2019, pp. 342–345, doi: 10.1109/IEDM19573.2019.8993509.

- [13] F.-C. Sun, M. T. Kesim, Y. Espinal, and S. P. Alpay, "Are ferroelectric multilayers capacitors in series," *J. Mater. Sci.*, vol. 51, no. 1, pp. 499–505, Jan. 2016, doi: 10.1007/s10853-015-9298-0.

- [14] Z. Liu, M. A. Bhuiyan, and T. P. Ma, "A critical examination of 'quasi-static negative capacitance'(QSNC) theory," in *IEDM Tech. Dig.*, Dec. 2018, pp. 711–714, doi: 10.1109/IEDM.2018.8614614.

- [15] M. Si, X. Lyu, and P. D. Ye, "Ferroelectric polarization switching of hafnium zirconium oxide in a ferroelectric/dielectric stack," ACS Appl. Electron. Mater., vol. 1, no. 5, pp. 745–751, May 2019, doi: 10.1021/acsaelm.9b00092.

- [16] A. Q. Jiang, H. J. Lee, G. H. Kim, and C. S. Hwang, "The inlaid Al<sub>2</sub>O<sub>3</sub> tunnel switch for ultrathin ferroelectric films," *Adv. Mater.*, vol. 21, no. 28, pp. 2870–2875, Jul. 2009, doi: 10.1002/adma.200802924.

- [17] Y. J. Kim et al., "Interfacial charge-induced polarization switching in Al<sub>2</sub>O<sub>3</sub>/Pb(Zr,Ti)O<sub>3</sub> bi-layer," J. Appl. Phys., vol. 118, no. 22, Dec. 2015, Art. no. 224105, doi: 10.1063/1.4937544.

- [18] N. Gong and T.-P. Ma, "A study of endurance issues in HfO<sub>2</sub>-based ferroelectric field effect transistors: Charge trapping and trap generation," *IEEE Electron Device Lett.*, vol. 39, no. 1, pp. 15–18, Jan. 2018, doi: 10.1109/LED.2017.2776263.

- [19] K. Ni *et al.*, "Critical role of interlayer in Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> ferroelectric FET nonvolatile memory performance," *IEEE Trans. Electron Devices*, vol. 65, no. 6, pp. 2461–2469, Jun. 2018, doi: 10.1109/TED.2018.2829122.

- [20] Y. Higashi *et al.*, "Impact of charge trapping on imprint and its recovery in HfO<sub>2</sub> based FeFET," in *IEDM Tech. Dig.*, Dec. 2019, pp. 358–361, doi: 10.1109/IEDM19573.2019.8993472.

- [21] K. Toprasertpong, M. Takenaka, and S. Takagi, "Direct observation of interface charge behaviors in FeFET by quasi-static split C-V and Hall techniques: Revealing FeFET operation," in *IEDM Tech. Dig.*, Dec. 2019, pp. 570–573, doi: 10.1109/IEDM19573.2019.8993664.

- [22] J. Li, Y. Qu, M. Si, X. Lyu, and P. D. Ye, "Multi-probe characterization of ferroelectric/dielectric interface by C-V, P-V and conductance methods," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2020, pp. 1–2.

- [23] K. Florent *et al.*, "Investigation of the endurance of FE-HfO<sub>2</sub> devices by means of TDDB studies," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Mar. 2018, pp. 6D.3-1–6D.3-7, doi: 10.1109/IRPS.2018.8353634.

[24] A. J. Tan *et al.*, "Hot electrons as the dominant source of degradation for

- [24] A. J. Tan *et al.*, "Hot electrons as the dominant source of degradation for sub-5 nm HZO FeFETs," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2020, pp. 3–7.

- [25] S. Salahuddin and S. Datta, "Use of negative capacitance to provide voltage amplification for low power nanoscale devices," *Nano Lett.*, vol. 8, no. 2, pp. 405–410, Feb. 2008, doi: 10.1021/nl071804g.

- [26] J. Zhou *et al.*, "Ferroelectric HfZrO<sub>X</sub> Ge and GeSn PMOSFETs with sub-60 mV/decade subthreshold swing, negligible hysteresis, and improved I<sub>ds</sub>," in *IEDM Tech. Dig.*, Dec. 2016, pp. 310–313, doi: 10.1109/IEDM.2016.7838401.

- [27] M. H. Lee *et al.*, "Physical thickness 1.X nm ferroelectric HfZrO<sub>x</sub> negative capacitance FETs," in *IEDM Tech. Dig.*, Dec. 2016, pp. 306–309, doi: 10.1109/IEDM.2016.7838400.

- [28] W. Chung, M. Si, and P. D. Ye, "Hysteresis-free negative capacitance germanium CMOS FinFETs with bi-directional sub-60 mV/dec," in *IEDM Tech. Dig.*, Dec. 2017, pp. 365–368, doi: 10.1109/IEDM.2017.8268395.

- [29] M. Si *et al.*, "Steep-slope hysteresis-free negative capacitance MoS<sub>2</sub> transistors," *Nature Nanotechnol.*, vol. 13, no. 1, pp. 24–28, Jan. 2018, doi: 10.1038/s41565-017-0010-1.

- [30] M. A. Alam, M. Si, and P. D. Ye, "A critical review of recent progress on negative capacitance field-effect transistors," *Appl. Phys. Lett.*, vol. 114, no. 9, Mar. 2019, Art. no. 090401, doi: 10.1063/ 1.5092684.

- [31] A. I. Khan, U. Radhakrishna, K. Chatterjee, S. Salahuddin, and D. A. Antoniadis, "Negative capacitance behavior in a leaky ferroelectric," *IEEE Trans. Electron Devices*, vol. 63, no. 11, pp. 4416–4422, Nov. 2016, doi: 10.1109/TED.2016.2612656.

- [32] Y. J. Kim *et al.*, "Time-dependent negative capacitance effects in Al<sub>2</sub>O<sub>3</sub>/BaTiO<sub>3</sub> bilayers," *Nano Lett.*, vol. 16, no. 7, pp. 4375–4381, Jul. 2016, doi: 10.1021/acs.nanolett.6b01480.

- [33] M. Hoffmann *et al.*, "Unveiling the double-well energy landscape in a ferroelectric layer," *Nature*, vol. 565, no. 7740, pp. 464–467, Jan. 2019, doi: 10.1038/s41586-018-0854-z.

- [34] K. D. Kim *et al.*, "Transient negative capacitance effect in atomic-layer-deposited Al<sub>2</sub>O<sub>3</sub>/Hf<sub>0.3</sub>Zr<sub>0.7</sub>O<sub>2</sub> bilayer thin film," *Adv. Funct. Mater.*, vol. 29, no. 17, Apr. 2019, Art. no. 1808228, doi: 10.1002/adfm.201808228.

- [35] C. Alessandri, P. Pandey, A. Abusleme, and A. Seabaugh, "Switching dynamics of ferroelectric Zr-doped HfO<sub>2</sub>," *IEEE Electron Device Lett.*, vol. 39, no. 11, pp. 1780–1783, Nov. 2018, doi: 10.1109/LED.2018.2872124.

- [36] M. Si et al., "Ultrafast measurements of polarization switching dynamics on ferroelectric and anti-ferroelectric hafnium zirconium oxide," *Appl. Phys. Lett.*, vol. 115, no. 7, Aug. 2019, Art. no. 072107, doi: 10.1063/1.5098786.

- [37] R. Ichihara *et al.*, "Re-examination of vth window and reliability in HfO<sub>2</sub> FeFET based on the direct extraction of spontaneous polarization and trap charge during memory operation," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2020, pp. 1–2.