## Effects of forming gas anneal on ultrathin InGaAs nanowire metal-oxide-semiconductor field-effect transistors

Cite as: Appl. Phys. Lett. 102, 093505 (2013); https://doi.org/10.1063/1.4794846 Submitted: 26 January 2013 . Accepted: 25 February 2013 . Published Online: 05 March 2013

Mengwei Si, Jiangjiang J. Gu, Xinwei Wang, Jiayi Shao, Xuefei Li, Michael J. Manfra, Roy G. Gordon, and Peide D. Ye

## ARTICLES YOU MAY BE INTERESTED IN

Effects of  $(NH_4)_2S$  passivation on the off-state performance of 3-dimensional InGaAs metal-oxide-semiconductor field-effect transistors

Applied Physics Letters 99, 152113 (2011); https://doi.org/10.1063/1.3651754

Impact of Fermi level pinning inside conduction band on electron mobility in InGaAs metaloxide-semiconductor field-effect transistors

Applied Physics Letters 103, 143509 (2013); https://doi.org/10.1063/1.4824474

Effect of annealing ambient and temperature on the electrical characteristics of atomic layer deposition  $Al_2O_3/In_{0.53}Ga_{0.47}As$  metal-oxide-semiconductor capacitors and MOSFETs

Journal of Applied Physics 111, 044105 (2012); https://doi.org/10.1063/1.3686628

## Effects of forming gas anneal on ultrathin InGaAs nanowire metal-oxide-semiconductor field-effect transistors

Mengwei Si,<sup>1</sup> Jiangjiang J. Gu,<sup>1</sup> Xinwei Wang,<sup>2,3</sup> Jiayi Shao,<sup>4</sup> Xuefei Li,<sup>1</sup> Michael J. Manfra,<sup>1,4,5</sup> Roy G. Gordon,<sup>2</sup> and Peide D. Ye<sup>1,a)</sup>

<sup>1</sup>School of Electrical and Computer Engineering and Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana 47907, USA

<sup>2</sup>Department of Chemistry and Chemical Biology, Harvard University, Cambridge, Massachusetts 02138, USA

<sup>3</sup>School of Advanced Materials, Peking University, Shenzhen Graduate School, Shenzhen 518055, China

<sup>4</sup>Department of Physics, Purdue University, West Lafayette, Indiana 47907, USA

(Received 26 January 2013; accepted 25 February 2013; published online 5 March 2013)

InGaAs gate-all-around metal-oxide-semiconductor field-effect transistors (MOSFETs) with 6 nm nanowire thickness have been experimentally demonstrated at sub-80 nm channel length. The effects of forming gas anneal (FGA) on the performance of these devices have been systematically studied. The 30 min 400 °C FGA (4%  $H_2/96\%$   $N_2$ ) is found to improve the quality of the  $Al_2O_3/InGaAs$  interface, resulting in a subthreshold slope reduction over  $20\,\text{mV/dec}$  (from  $117\,\text{mV/dec}$  in average to  $93\,\text{mV/dec}$ ). Moreover, the improvement of interface quality also has positive impact on the on-state device performance. A scaling metrics study has been carried out for FGA treated devices with channel lengths down to  $20\,\text{nm}$ , indicating excellent gate electrostatic control. With the FGA passivation and the ultra-thin nanowire structure, InGaAs MOSFETs are promising for future logic applications. ©  $2013\,\text{American Institute of Physics}$ . [http://dx.doi.org/10.1063/1.4794846]

Recently, InGaAs has been considered as one of the promising channel materials for CMOS beyond the 10 nm technology node because of its large electron mobility. 3D InGaAs devices such as fin field-effect transistors and the gate-all-around (GAA) metal-oxide-semiconductor field effect transistors have been shown to offer large drive current and excellent immunity to short channel effects (SCE).<sup>1-6</sup> In particular, the GAA MOSFETs provide the best gate electrostatic control and therefore the ultimate channel length  $(L_{ch})$  scalability. It is known that better SCE control can be obtained by reducing the nanowire size, enabling further  $L_{ch}$  scaling. InGaAs nanowires fabricated by top-down technology with sub-10 nm wire dimension, either nanowire width  $(W_{NW})$  or thickness  $(T_{NW})$ , have not been reported. On the other hand, the interface quality is one of the critical problems for III-V MOSFETs. Superior interface quality is required for optimizing both the on-state and off-state performance of MOSFETs. Al<sub>2</sub>O<sub>3</sub> is commonly used as the gate insulator for InGaAs MOSFETs for the relatively low interface trap density  $(D_{it})$ . Various passivation methods have been developed and optimized on the Al<sub>2</sub>O<sub>3</sub>/InGaAs interface such as (NH<sub>4</sub>)<sub>2</sub>S passivation, 7,8 surface nitridation, 9,10 and phosphor passivation. 11 Forming gas anneal is another common post metallization treatment used to improve the interface quality of Al<sub>2</sub>O<sub>3</sub>/InGaAs. Interface traps, oxide charges, and border traps reduction after FGA have been reported by CV methods. 12,13 Recent study of effects of FGA on planar devices shows that on-state performances such as drive current (I<sub>on</sub>) and transconductance (g<sub>m</sub>) are improved after FGA.<sup>14</sup> However, the impacts of FGA have not been studied in short channel devices with GAA

structure. The compatibility between FGA and other passivation methods have not been studied either.

In this letter, 20–80 nm  $L_{ch}$  short channel In<sub>0.65</sub>Ga<sub>0.35</sub>As GAA MOSFETs with 6 nm  $T_{NW}$  and 30 nm  $W_{NW}$  have been fabricated with or without FGA treatment. FGA offers improvement in the on-state and off-state performance of the devices. The reduction of subthreshold slope (SS) and the increase of gm and Ion verify the improvement of the interface quality. The average interface trap density drops by 40% on average after FGA. Moreover, SS and drain induced barrier lowering (DIBL) do not increase when  $L_{ch}$  scales from 80 nm down to 20 nm, demonstrating the excellent scalability of InGaAs GAA MOSFET with sub-10 nm nanowire dimension. It is also found that the 30 min 400 °C FGA passivation is fully compatible with the (NH<sub>4</sub>)<sub>2</sub>S passivation. The interface trap density is significantly improved in devices with (NH<sub>4</sub>)<sub>2</sub>S passivation and FGA together than those with  $(NH_4)_2S$  passivation only.

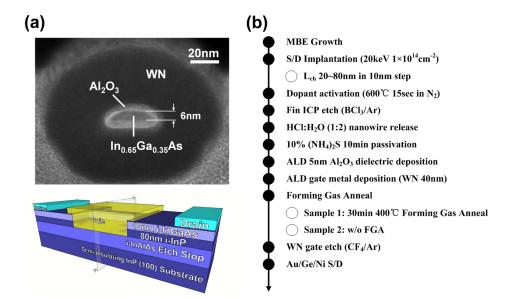

Figure 1(a) shows the schematic diagram of the InGaAs GAA MOSFET fabricated in this work and the cross sectional transmission electron microscope (TEM) image of an InGaAs nanowire with 6 nm  $T_{NW}$ . The fabrication process flow of the devices is shown in Figure 1(b). The top-down fabrication process is similar to that demonstrated in Ref. 4. The starting material is a 2 in. semi-insulating InP substrate.  $100 \,\mathrm{nm}$  undoped  $\mathrm{In}_{0.52}\mathrm{Al}_{0.48}\mathrm{As}$  etch stop layer,  $80 \,\mathrm{nm}$ undoped InP layer, 10 nm undoped In<sub>0.65</sub>Ga<sub>0.35</sub>As channel layer, and 2 nm undoped InP layer were sequentially grown by molecular beam epitaxy. Source/drain implantation was performed at an energy of 20 keV and a dose of  $10^{14}$  cm<sup>-2</sup>, followed by dopant activation at 600 °C for 15 s in nitrogen ambient. After fabricating nanowire fins using BCl<sub>3</sub>/Ar reactive ion etching, HCl based release process was performed to create the free-standing InGaAs nanowires. Before the gate

<sup>&</sup>lt;sup>5</sup>School of Materials Engineering, Purdue University, West Lafayette, Indiana 47907, USA

a) Author to whom correspondence should be addressed. Electronic mail: yep@purdue.edu.

FIG. 1. (a) Cross sectional TEM image and schematic diagram of an InGaAs GAA MOSFET with  $T_{\rm NW}\!=\!6\,{\rm nm}$ . (b) Fabrication process flow of the InGaAs GAA MOSFETs.

stack deposition,  $10\%~(NH_4)_2S$  passivation was performed. The gate dielectric is 5 nm atomic layer deposited (ALD)  $Al_2O_3$  to study the effect of FGA on  $Al_2O_3$ /InGaAs interface while maintaining a low gate leakage current. Following ALD WN gate metallization process, the devices are divided into two groups. One was treated with  $30\,\text{min}~400\,^\circ\text{C}$  FGA (4%  $H_2/96\%~N_2$ ) and the other served as the control group. After gate etch process, source/drain contacts were formed with Au/Ge/Ni alloy. Each device has four nanowires fabricated in parallel. All patterns were defined by a Vistec UHR electron beam lithography system.

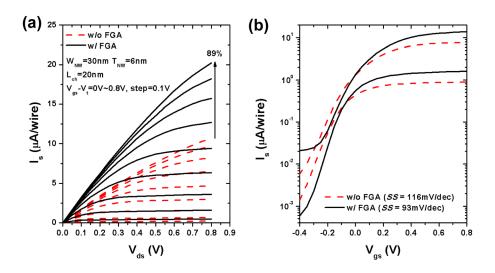

Figures 2(a) and 2(a) show the I-V characteristics comparison between two typical devices with  $L_{\rm ch}=20\,{\rm nm},$   $W_{\rm NW}=30\,{\rm nm}$  with and without  $30\,{\rm min}$   $400\,^{\circ}{\rm C}$  FGA. Device with FGA shows an 89% increase in on-current (I\_{on}) at  $V_{\rm ds}=V_{\rm gs}-V_{\rm T}=0.8\,{\rm V}$  and the SS of device with FGA is  $93\,{\rm mV/dec}$ , which is  $23\,{\rm mV/dec}$  smaller than that of device without FGA. Maximum  $g_{\rm m}$  of device with FGA is also found to be 59% larger than that of control device without FGA. After being normalized by the perimeter of the nanowire, the best  $I_{\rm on}$  and peak  $g_{\rm m}$  at  $V_{\rm ds}=V_{\rm gs}-V_{\rm T}=1\,{\rm V}$  is  $505\,\mu{\rm A/\mu m}$  and  $665\,\mu{\rm S/um}$ , respectively. The saturation-currents of devices in this work are lower compared to InGaAs GAA MOSFETs with  $30\,{\rm nm}$   $T_{\rm NW}$  and the same

W<sub>NW</sub> and L<sub>ch</sub>. The reduction in drive current is attributed to the larger impact of surface roughness which decreases the channel mobility. Details of the transport properties of the ultra-thin nanowires are under investigation.

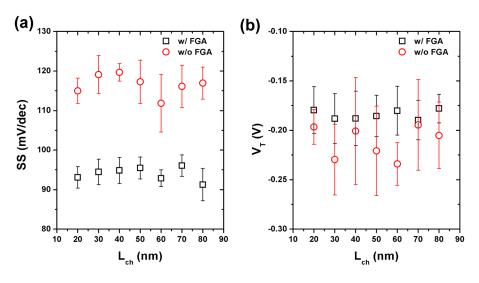

To study the effects of FGA, the average SS, threshold voltage V<sub>T</sub>, and I<sub>on</sub> of InGaAs GAA MOSFETs with L<sub>ch</sub> between 20 nm and 80 nm have been extracted. Figures 3(a), 3(b), and 4(a) show the statistical data of SS, V<sub>T</sub> and I<sub>on</sub> for devices with and without FGA. As shown in Figure 3(a), devices with FGA has a much lower SS for all channel lengths compared to the control devices without FGA. The average of SS shows an obvious reduction from about 117 mV/dec to 93 mV/dec. The improvement of off-state performance indicates that FGA can reduce the interface traps within the bandgap. The threshold voltage is found to increase with FGA treatment, as shown in Figure 3(b). It is known that traps at the Al<sub>2</sub>O<sub>3</sub>/InGaAs interface are mostly donor type. The reduction of donor interface trap does not have a significant impact on the threshold voltage while the reduction of acceptor trap leads to negative V<sub>T</sub> shift. <sup>15</sup> Thus, the positive shift of V<sub>T</sub> in this study is attributed to the reduction of positive fixed charge density and the ion charge density in oxide layer. Figure 4(a) shows the comparison of on-current. Ion is found to increase by 14% on average with

FIG. 2. (a) Output and (b) transfer characteristics of two typical InGaAs GAA MOSFETs with  $L_{\rm ch}\!=\!20\,{\rm nm},~W_{\rm NW}\!=\!30\,{\rm nm},$  and  $T_{\rm NW}\!=\!6\,{\rm nm}$  with and without FGA treatment. Due to the significant reverse junction leakage current,  $I_S$  is presented instead of  $I_D$ .

FIG. 3. (a) SS and (b)  $V_T$  of these devices with  $W_{NW} = 30\,\mathrm{nm}$  and  $T_{NW} = 6\,\mathrm{nm}$  versus  $L_{\mathrm{ch}}$ . With FGA and their control devices are in comparison. Each data point represents 5–10 measured devices.  $V_T$  is extracted from linear extrapolation at  $V_{ds} = 50\,\mathrm{mV}$ .

FGA, accompanied by 25%  $g_{\rm m}$  enhancement (not shown). One origin for the  $I_{\rm on}$  enhancement is the reduction of interface trap density near the conduction band edge. Another origin is that mobility is improved due to the reduction in Coulomb scattering as a result of oxide charge reduction.

Interface trap density of the devices are extracted with the approximate formula  $SS = 60(1 + (qD_{it} + C_D)/C_{ox}) \, mV/dec$ ,  $^{16}$  where  $C_D$  is the depletion capacitance and  $C_{ox}$  is the gate capacitance. The depletion capacitance can be neglected for its weak impact on SS. Devices in Ref. 4 show the minimum SS of 63 mV/dec, which indicates  $C_D$  contribute to at most 3 mV/dec to SS in the InGaAs GAA MOSFET structure. As the device structure is similar as Ref. 4,  $C_D$  is also negligible in this work. Thus, subthreshold swing can be written as  $SS = 60(1 + qD_{it}/C_{ox}) \, mV/dec$ . It is estimated that the upper limit of mid-gap  $D_{it}$  is reduced by 40% percent with FGA, indicating that FGA can improve the interface quality of the  $Al_2O_3/InGaAs$  interface.

Another interesting phenomenon found in this work is the standard deviation (STD) comparison for SS,  $V_T$ , and  $I_{\rm on}$ . The SS STD and  $V_T$  STD of devices with FGA are smaller than the control devices without FGA, while the  $I_{\rm on}$  STD and  $g_{\rm m}$  STD of devices with FGA are larger than devices without FGA. The STD of SS and  $V_T$  reduces with FGA treatment because of the improvement of the interface quality as shown

earlier. However, the larger on-state STD seems unexpected and contradictory to the Dit reduction. The most possible reason is that the ohmic contact of the devices with FGA is worse than those without FGA, which can in turn increase on-state variation. To confirm this hypothesis, external resistance ( $R_{ext}$ ) is extracted by linear fitting  $R_{tot}$  and  $1/(V_{gs}-V_T-V_{ds}/2)$  at small  $V_{ds}$ . As shown in Figure 4(b), both average value of  $R_{ext}$  and STD of  $R_{ext}$  of devices with FGA is much larger than devices without FGA. The larger R<sub>ext</sub> of devices with FGA suggests that the intrinsic current improvement of devices with FGA is even larger than that shown in Figure 4(a). Although the exact reason for the increased R<sub>ext</sub> after FGA has not been clearly understood, it is likely that the Au/Ge/Ni alloy based ohmic contact is sensitive to FGA treatment. More advanced source/drain contact technologies need to be explored to reduce the R<sub>ext</sub> and improve on-state variation.

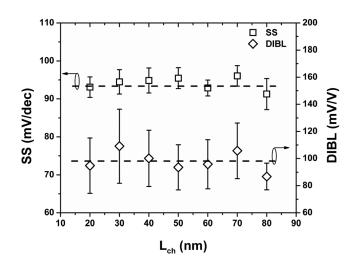

Furthermore, we investigate the scaling metrics of InGaAs GAA MOSFETs with 6 nm  $T_{\rm NW}$  and FGA. The  $T_{\rm NW}$  scaling of an InGaAs GAA MOSFET theoretically has the same effect as the  $W_{\rm NW}$  scaling in terms of the electrostatic control.<sup>4</sup> However, the scaling of  $T_{\rm NW}$  can reduce the surface area that has underwent dry etching process during the nanowire formation, leading to the reduced surface roughness. Figure 5 shows SS and DIBL versus  $L_{\rm ch}$  with  $W_{\rm NW}=30\,{\rm nm}$ .

FIG. 4. (a)  $I_{on}$  and (b)  $R_{ext}$  versus  $L_{ch}$  in comparison between FGA devices and their control ones

FIG. 5. SS and DIBL versus  $L_{ch}$  of FGA treated InGaAs GAA MOSFETs with  $W_{\rm NW}\!=\!30\,\text{nm}$  and  $T_{\rm NW}\!=\!6\,\text{nm}.$

No evidence of  $L_{ch}$  dependence of SS and DIBL are observed in this work, as opposed to the InGaAs GAA MOSFETs with larger  $T_{NW}$ . The results show that the InGaAs GAA MOSFETs with extremely thin  $T_{NW}$  offer better immunity to SCE and improved scalability which can be further improved by equivalent oxide thickness (EOT) scaling.  $^{4,18,19}$

In conclusion, InGaAs GAA MOSFETs with 6 nm T<sub>NW</sub> have been fabricated. The effects of FGA on the performance of the devices are systematically studied. It is found that the 30 min 400 °C forming gas anneal results in an improved Al<sub>2</sub>O<sub>3</sub>/InGaAs interface and is also fully compatible with the (NH<sub>4</sub>)<sub>2</sub>S passivation. A scaling metrics study of the InGaAs GAA MOSFETs has also been carried out. The extremely thin nanowire structure has been shown to improve SCE immunity, and it is very promising for future logic applications.

The authors would like to thank D. A. Antoniadis, J. A. del Alamo, and M. S. Lundstrom for valuable discussions. This work is supported by SRC FCRP MSD Center and AFOSR, monitored by Professor James C. M. Hwang.

- <sup>1</sup>J. J. Gu, Y. Q. Liu, Y. Q. Wu, R. Colby, R. G. Gordon, and P. D. Ye, in 2011 IEEE International Electron Devices Meeting (IEDM), Washington, DC, 5–7 December 2011, p. 769.

- <sup>2</sup>M. Radosavljevic, G. Dewey, D. Basu, J. Boardman, B. Chu-Kung, J. M. Fastenau, S. Kabehie, J. Kavalieros, V. Le, and W. K. Liu, in 2011 IEEE International Electron Devices Meeting (IEDM), Washington, DC, 5–7 December 2011, p. 765.

- <sup>3</sup>H. C. Chin, X. Gong, L. Wang, H. K. Lee, L. Shi, and Y. C. Yeo, IEEE Electron Device Lett. **32**, 146 (2011).

- <sup>4</sup>J. J. Gu, X. W. Wang, H. Wu, J. Shao, A. T. Neal, M. J. Manfra, R. G. Gordon, and P. D. Ye, in 2012 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 10–12 December 2012, p. 633.

- <sup>5</sup>F. Xue, A. Jiang, Y.-T. Chen, Y. Wang, F. Zhou, Y.-F. Chang, and J. Lee, in 2012 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 10–12 December 2012, p. 629.

- <sup>6</sup>Y. Q. Wu, R. S. Wang, T. Shen, J. J. Gu, and P. D. Ye, in 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, 7–9 December 2009, p. 331.

- <sup>7</sup>É. O'Connor, B. Brennan, V. Djara, K. Cherkaoui, S. Monaghan, S. B. Newcomb, R. Contreras, M. Milojevic, G. Hughes, and M. E. Pemble, J. Appl. Phys. **109**, 024101 (2011).

- <sup>8</sup>J. J. Gu, A. T. Neal, and P. D. Ye, Appl. Phys. Lett. **99**, 152113 (2011).

- <sup>9</sup>F. Capasso and G. F. Williams, J. Electrochem. Soc. **129**(4), 821 (1982).

- <sup>10</sup>T. Hoshii, S. Lee, R. Suzuki, N. Taoka, M. Yokoyama, H. Yamada, M. Hata, T. Yasuda, M. Takenaka, and S. Takagi, J. Appl. Phys. 112, 073702 (2012).

- <sup>11</sup>J. Lin, S. Lee, H. J. Oh, W. Yang, G. Q. Lo, D. L. Kwong, and D. Z. Chi, in 2008 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 15–17 December 2008, p. 401.

- <sup>12</sup>B. Shin, J. R. Weber, R. D. Long, P. K. Hurley, C. G. Van de Walle, and P. C. McIntyre, Appl. Phys. Lett. **96**, 152908 (2010).

- <sup>13</sup>E. J. Kim, L. Wang, P. M. Asbeck, K. C. Saraswat, and P. C. McIntyre, Appl. Phys. Lett. **96**, 012906 (2010).

- <sup>14</sup>V. Djara, K. Cherkaoui, M. Schmidt, S. Monaghan, E. O'Connor, I. M. Povey, D. O'Connell, M. E. Pemble, and P. K. Hurley, IEEE Trans. Electron Devices 59, 1084 (2012).

- <sup>15</sup>D. Varghese, Y. Xuan, Y. Q. Wu, T. Shen, P. D. Ye, and M. A. Alam, in 2008 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 15–17 December 2008, p. 379.

- <sup>16</sup>S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices* (Wiley-Interscience, 2006).

- <sup>17</sup>P. Hashemi, L. Gomez, and J. L. Hoyt, IEEE Electron Device Lett. 30, 401 (2009).

- <sup>18</sup>J. Lin, D. A. Antoniadis, and J. A. del Alamo, in 2012 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 10–12 December 2012 p. 757

- <sup>19</sup>D.-H. Kim, P. Hundal, A. Papavasiliou, P. Chen, C. King, J. Paniagua, M. Urteaga, B. Brar, Y. G. Kim, J.-M. Kuo, J. Li, P. Pinsukanjana, and Y. C. Kao, in 2012 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 10–12 December 2012, p. 761.