# Enhancement-mode atomic-layer thin In<sub>2</sub>O<sub>3</sub> transistors with maximum current exceeding 2 A/mm at drain voltage of 0.7 V enabled by oxygen plasma treatment ©

Cite as: Appl. Phys. Lett. **118**, 052107 (2021); https://doi.org/10.1063/5.0039783 Submitted: 06 December 2020 . Accepted: 18 January 2021 . Published Online: 05 February 2021

🗓 Adam Charnas, 🗓 Mengwei Si, Zehao Lin, and 🗓 Peide D. Ye

# **COLLECTIONS**

F This paper was selected as Featured

# **ARTICLES YOU MAY BE INTERESTED IN**

Perspective on ferroelectric, hafnium oxide based transistors for digital beyond von-Neumann computing

Applied Physics Letters 118, 050501 (2021); https://doi.org/10.1063/5.0035281

How good are 2D transistors? An application-specific benchmarking study Applied Physics Letters 118, 030501 (2021); https://doi.org/10.1063/5.0029712

Intense and recoverable piezoluminescence in Pr<sup>3+</sup>-activated CaTiO<sub>3</sub> with centrosymmetric structure

Applied Physics Letters 118, 053901 (2021); https://doi.org/10.1063/5.0039360

# Enhancement-mode atomic-layer thin In<sub>2</sub>O<sub>3</sub> transistors with maximum current exceeding 2 A/mm at drain voltage of 0.7 V enabled by oxygen plasma treatment ()

Cite as: Appl. Phys. Lett. 118, 052107 (2021); doi: 10.1063/5.0039783 Submitted: 6 December 2020 · Accepted: 18 January 2021 · Published Online: 5 February 2021

Adam Charnas,<sup>1,2</sup> (b) Mengwei Si,<sup>1,2</sup> (b) Zehao Lin,<sup>1,2</sup> and Peide D. Ye<sup>1,2,a)</sup> (b)

School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana 47907, USA

# **ABSTRACT**

In this Letter, enhancement-mode operation in devices with 1.5 nm atomic-layer thin In<sub>2</sub>O<sub>3</sub> channels over a wide range of channel lengths down to 40 nm is demonstrated using an O<sub>2</sub> plasma treatment at room temperature. Drain currents (I<sub>D</sub>) in excess of 2 A/mm at a drain-to-source bias (VDS) of 0.7 V are achieved in enhancement mode with significantly improved subthreshold swing down to near-ideal 65 mV/dec, suggesting that O2 plasma treatment is very effective at reducing bulk and interface defects. By using low-temperature O2 plasma, the fabrication process remains back-end-of-line compatible while enabling a clear route toward high-performance In<sub>2</sub>O<sub>3</sub> transistors and circuitry.

Published under license by AIP Publishing. https://doi.org/10.1063/5.0039783

Ultra-thin atomic-layer-deposited (ALD) In<sub>2</sub>O<sub>3</sub><sup>1-3</sup> has recently been explored for high-performance back-end-of-line (BEOL) compatible electronic devices<sup>4–11</sup> for monolithic 3D integration. Using the asgrown In<sub>2</sub>O<sub>3</sub> channels with no further treatment, the threshold voltage (V<sub>T</sub>) in buried-gate field-effect transistors (FETs) is a strong function of the channel thickness (T<sub>CH</sub>) and the best performing devices are restricted to depletion-mode operation. 1,2 This is an undesirable tradeoff, and a separate method is needed to engineer V<sub>T</sub>. An annealing process can induce the desired V<sub>T</sub> shift, but comes at the cost of increased thermal budget, which may not be tolerable for all applications.<sup>3</sup> Here, we resolve this trade-off by introducing a simple process at the end of the device fabrication. By treating the devices with an O2 plasma at room temperature, V<sub>T</sub> can be engineered while maintaining the low thermal budget and, thus, the BEOL compatibility of the process.

Devices treated with O<sub>2</sub> plasma for different amounts of time are demonstrated and analyzed over a wide range of channel lengths  $(L_{CH})$  from 1  $\mu$ m to 40 nm. As in the previous work, the scaled devices are able to conduct drain currents well in excess of 2 A/mm, but now operate in enhancement mode enabled by controllably shifting V<sub>T</sub>, making them highly attractive for BEOL transistor and circuitry applications. Furthermore, the subthreshold swing (SS) is improved

significantly down to near-ideal 65 mV/dec, closely approaching the thermionic limit at room temperature, corresponding to a low interface trap density ( $D_{it}$ ) of  $8 \times 10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$ .

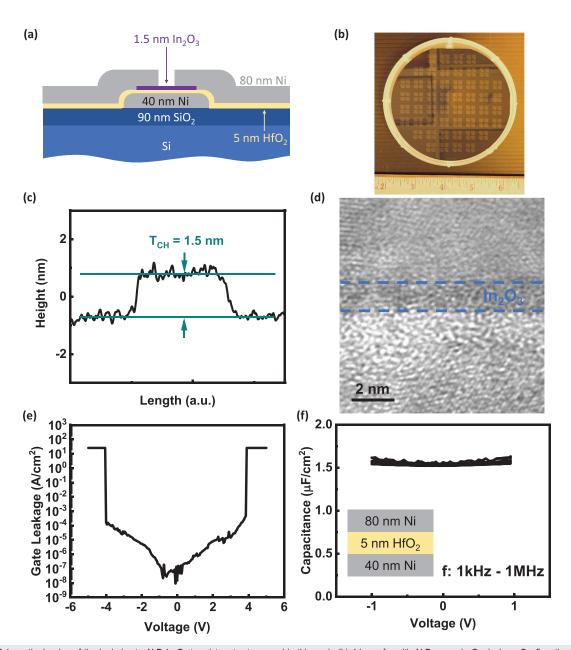

In2O3 transistors were fabricated as described in detail in an earlier publication.<sup>1</sup> A buried-gate FET structure [more specifically, a staggered bottom-gate thin-film transistor (TFT) structure] is employed with Ni serving as the gate, source, and drain electrodes. The 5 nm HfO<sub>2</sub> layer used as the gate dielectric and the 1.5 nm thick In<sub>2</sub>O<sub>3</sub> channel layer are grown by ALD, using [(CH<sub>3</sub>)<sub>2</sub>N]<sub>4</sub>Hf (TDMAHf) and (CH<sub>3</sub>)<sub>3</sub>In (TMIn) as the respective metal-organic precursors and H<sub>2</sub>O as the oxygen source for both materials. HfO<sub>2</sub> and In<sub>2</sub>O<sub>3</sub> were grown at 200 °C and 225 °C, respectively. An illustration of the final structure is shown in Fig. 1(a). Figure 1(b) shows a 4-in. wafer of In<sub>2</sub>O<sub>3</sub> devices, enabled by the large-scale uniform ALD growth. Figures 1(c) and 1(d) demonstrate accurate thickness control of the In<sub>2</sub>O<sub>3</sub> channel by ALD cycles using atomic force microscopy (AFM) and transmission electron microscopy (TEM), respectively. Figure 1(e) presents a breakdown measurement of the gate dielectric showing a hard breakdown voltage around 4 V, confirming the high quality of ALD HfO2 on Ni. Figure 1(f) shows C-V measurements used to extract the equivalent oxide thickness (EOT) and directly

<sup>&</sup>lt;sup>2</sup>Birck Nanotechnology Center, Purdue University, West Lafayette, Indiana 47907, USA

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed: yep@purdue.edu

FIG. 1. (a) Schematic drawing of the buried-gate ALD  $In_2O_3$  transistor structure used in this work. (b) 4-in. wafer with ALD-grown  $In_2O_3$  devices. Confirmation of good ALD thickness control by (c) AFM measurement of 1.5-nm-thick  $In_2O_3$  and (d) TEM of a 1.2-nm-thick ALD  $In_2O_3$  layer. (e) Breakdown test of the HfO<sub>2</sub> gate dielectric. (f) C-V measurement used to extract EOT. The inset shows the test structure used for (e) and (f).

measure the gate oxide capacitance ( $C_{\rm ox}$ ). The EOT is 2.1 nm. After the structural fabrication was complete, the devices were exposed to an  $O_2$  plasma generated with an RF power of 100 W at 1.25 Torr in a barrel asher at room temperature. Depending on the length of plasma exposure,  $V_{\rm T}$  can be controllably tuned. Since the plasma treatment is performed after fabrication, the excellent contact resistance between Ni and the degenerately n-type native  $In_2O_3$  under the contacts<sup>2</sup> is maintained, while the channel properties are modified. The process remains BEOL compatible due to the low-temperature nature of the  $O_2$  plasma.

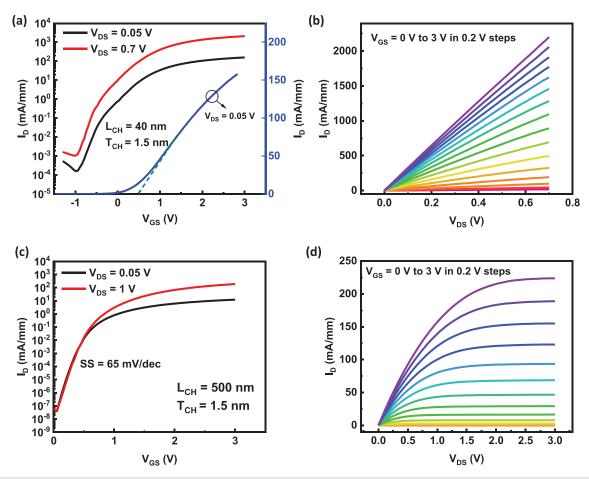

Transfer ( $I_D$ – $V_{GS}$ ) and output ( $I_D$ – $V_{DS}$ ) characteristics of typical short- and long-channel transistors after a 10-min  $O_2$  plasma treatment are shown in Fig. 2. In both cases,  $V_T$  is greater than 0 V, and the dependence on  $L_{CH}$  is weakened, which can be attributed to a reduction in the intrinsic electron doping by defects. <sup>12</sup> Figures 2(a) and 2(b) show curves for a device with  $L_{CH}$  = 40 nm. The maximum on-current reaches 2.2 A/mm at a drain bias of 0.7 V and an overdrive voltage of 2.44 V ( $V_T$  is 0.56 V).  $V_T$  is determined by the linear extrapolation method. The longer channel device measured in Figs. 2(c)

FIG. 2. Transfer and output characteristics of typical (a) and (b) 40 nm and (c) and (d) 500 nm channel length  $ln_2O_3$  transistors after  $O_2$  plasma treatment for 10 min (1.25 Torr, 100 W RF power at room temperature). The  $ln_2O_3$  channel layer is 1.5 nm thick. The 40 nm devices achieve on-currents of 2.2 A/mm at a moderate drain bias of 0.7 V and operate in enhancement mode; the device shown has  $V_T = 0.56$  V. The 500 nm device shown has a near-ideal SS of 65 mV/dec.

and 2(d) with  $L_{CH}\!=\!500\,\text{nm}$  shows saturation behavior at high  $V_{DS}$  with a near-ideal SS of 65 mV/dec. The interface trap density  $(D_{it})$  at the  $HfO_2/In_2O_3$  interface can be estimated to be  $8\times10^{11}\,\text{cm}^{-2}\,\text{eV}^{-1}$  according to SS = 2.3 kT/q (1 +  $C_{it}/C_{ox}$ ), where k is the Boltzmann constant and q is the elementary charge. The impact of depletion capacitance is negligible due to the ultrathin nature of the  $In_2O_3$  channel.

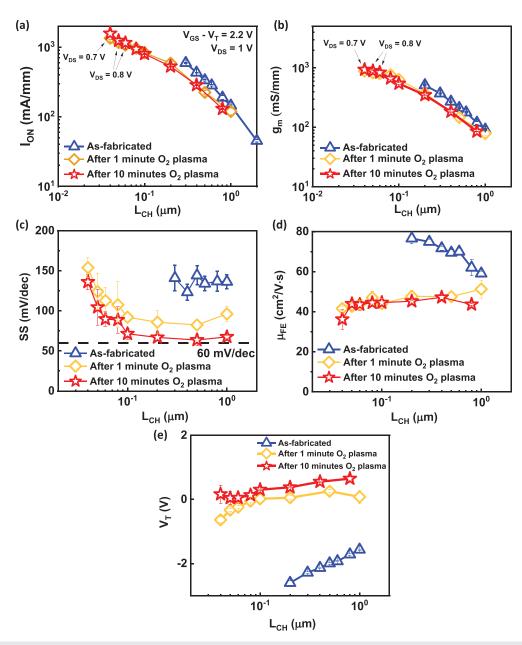

Figure 3 shows key device performance metrics as a function of channel length for three different cases: (i) no  $O_2$  plasma treatment, (ii) a moderate duration  $O_2$  plasma treatment (1 min), and (iii) a longer  $O_2$  plasma treatment (10 min). All  $O_2$  plasma treatments were performed in an atmosphere of 1.25 Torr  $O_2$  with an applied RF power of 100 W at room temperature. Figure 3(a) shows the average on-current ( $I_{ON}$ ) at a constant gate overdrive voltage of 2.2 V achieved at a drainsource bias ( $V_{DS}$ ) of 1 V (except where otherwise noted). At a given  $I_{CH}$ ,  $I_{ON}$  is moderately reduced after plasma treatment. However, the currents are still so large that they push the limits of the material system—for the shortest channel lengths explored in this work, a reduced  $I_{OS}$  must be applied to avoid self-heating effects. Figure 3(b) shows the transconductance ( $I_{OS}$ ) likewise reduced by a moderate

amount in  $O_2$  plasma-treated devices compared to their counterparts at the same  $L_{\rm CH}$ . This may be due to the reduced carrier concentration in the channel increasing the channel resistance. Similarly, Fig. 3(d) shows a reduction in  $\mu_{\rm FE}$  since it is extracted from  $g_{\rm m}$ . The positive  $V_{\rm T}$  shift enables the channel length scaling down to 40 nm. As a result, a high  $g_{\rm m}$  value of 0.94 S/mm at a  $V_{\rm DS}$  value of 0.7 V is achieved. Figure 3(c) shows the SS significantly improving as a longer  $O_2$  plasma treatment is applied, closely approaching the room-temperature thermionic limit of 60 mV/dec in long-channel devices. This suggests a sizeable interface and bulk trap density in the as-grown In<sub>2</sub>O<sub>3</sub> film has been reduced by the  $O_2$  plasma treatment. Figure 3(e) shows  $V_{\rm T}$  at each measured channel length. After a sufficiently long  $O_2$  plasma exposure, the devices all operate in enhancement mode.

Although there are competing theories, it has long been thought that oxygen vacancies play a crucial role in indium oxide's electrical properties, e.g., Refs. 13–15. The specific TMIn/H<sub>2</sub>O ALD chemistry employed in this work has been studied<sup>16,17</sup> and shows the same vacancy doping behavior as other growth methods. A similar O<sub>2</sub> plasma treatment has been studied by x-ray photoelectron spectroscopy (XPS) in much thicker (500–1000 nm) In<sub>2</sub>O<sub>3</sub> layers grown by

**FIG. 3.** (a) Average on-current for each channel length at a constant overdrive voltage of 2.2 V, with  $V_{DS} = 1$  V except for the devices indicated. (b)–(e) Transconductance, SS,  $\mu_{FE}$ , and  $V_{T}$  as functions of channel length under different plasma treatment conditions. With a sufficient  $O_2$  plasma exposure, devices at all measured channel lengths operate in enhancement mode and show a weaker  $V_{T}$ – $L_{CH}$  dependence.

plasma-assisted molecular beam epitaxy (MBE). A thin layer of charge is known to exist at the surfaces of (crystalline)  $In_2O_3$ . After their plasma treatment, significant band bending (away from being degenerately n-type) in the first few nanometers below the  $In_2O_3$  surface is extracted from the XPS measurements. While the mechanism responsible is not entirely clear, this provides some further insight into the behavior. Taken together with our device data, this paints a picture of the intrinsic defects that give  $In_2O_3$  such high electron doping and high current

densities, which is appreciably removed or filled by the energetic  $O_2$  from the plasma.

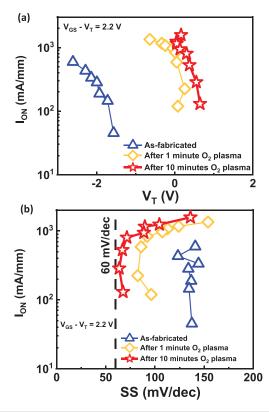

Figure 4 emphasizes the device parameters achieved in this work critical for high-performance device applications. Figure 4(a) shows the enhancement-mode operation of the devices across the measured range of channel lengths while simultaneously reaching over 2 A/mm of on-current. After a short exposure of 1 min, the devices are already close to their terminal  $V_{\rm T}$  values, suggesting a saturation of the  $O_2$  plasma effect near  $V_{\rm T}=0$  V, which allows for facile controllability and

**FIG. 4.** Comparisons of key device parameter evolution during  $O_2$  plasma treatment. (a)  $V_T$  is shifted while maintaining excellent  $I_{ON}$ . (b) Low SS near the thermionic limit is achieved in devices with high  $I_{ON}$  around 1 A/mm in enhancement-mode operation after sufficient treatment.

repeatability. Figure 4(b) shows an  $I_{ON}$ -SS plot, showing nearly ideal SS at currents approaching  $1\,A/mm$  in enhancement-mode  $In_2O_3$  devices treated with  $O_2$  plasma.

${

m O_2}$  plasma treatment of atomic-layer thin  ${

m In_2O_3}$  transistors has been demonstrated as an important process for engineering device behavior in a BEOL-compatible manner. The large controllable  ${

m V_T}$  shifts induced by the treatment are used to operate in enhancement mode with a 1.5-nm-thick  ${

m In_2O_3}$  channel down to the channel length of 40 nm while simultaneously improving the SS. Although at a given channel length, the on-current,  ${

m g_m}$ , and  ${

m \mu_{FE}}$  are reduced, overall performance is still the best for oxide semiconductors achieving an  ${

m I_D}$  value of 2.2 A/mm at  ${

m V_{DS}}$  = 0.7 V. This work provides a clear route to

apply recent work on atomic-layer thin channel  ${\rm In_2O_3}$  transistors for BEOL transistor and circuitry applications.

The authors gratefully acknowledge X. Sun and H. Wang for the technical support on TEM imaging. This work was mainly supported by the Semiconductor Research Corporation (SRC) through the nCore IMPACT Center. This work was also supported in part by AFOSR and SRC/DARPA JUMP ASCENT Center.

# **DATA AVAILABILITY**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

# **REFERENCES**

- <sup>1</sup>M. Si, Z. Lin, A. Charnas, and P. D. Ye, IEEE Electron Device Lett. (published online, 2020)

- <sup>2</sup>M. Si, Y. Hu, Z. Lin, X. Sun, A. Charnas, D. Zheng, X. Lyu, H. Wang, K. Cho, and P. D. Ye, Nano Lett. 21, 500 (2021).

- <sup>3</sup>M. Si, A. Charnas, Z. Lin, and P. D. Ye, IEEE Trans. Electron Devices (not published).

- <sup>41</sup>T. Kamiya, K. Nomura, and H. Hosono, Sci. Technol. Adv. Mater. 11, 044305 (2010).

- <sup>5</sup>K. Nomura, A. Takagi, T. Kamiya, H. Ohta, M. Hirano, and H. Hosono, Jpn. J. Appl. Phys., Part 1 45, 4303 (2006).

- <sup>6</sup>J. Wu, F. Mo, T. Saraya, T. Hiramoto, and M. Kobayashi, in Symposium on VLSI Technology (2020), p. THL.4.

- 7S. Samanta, K. Han, C. Sun, C. Wang, A. V. Thean, and X. Gong, in Symposium on VLSI Technology (2020), p. TH2.3.

- <sup>8</sup>S. Li, M. Tian, Q. Gao, M. Wang, T. Li, Q. Hu, X. Li, and Y. Wu, Nat. Mater. 18, 1091 (2019).

- <sup>9</sup>M. Si, J. Andler, X. Lyu, C. Niu, S. Datta, R. Agrawal, and P. D. Ye, ACS Nano 14, 11542 (2020).

- <sup>10</sup>W. Chakraborty, B. Grisafe, H. Ye, I. Lightcap, K. Ni, and S. Datta, in Symposium on VLSI Technology (2020), p. TH2.1.

- <sup>11</sup>H. Fujiwara, Y. Sato, N. Saito, T. Ueda, and K. Ikeda, in Symposium on VLSI Technology (2020), p. TH2.2.

- <sup>12</sup>S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*, 3rd ed. (Wiley, Hoboken, NJ, 2007), p. 332.

- <sup>13</sup>O. Bierwagen, Semicond. Sci. Technol. **30**, 024001 (2015).

- <sup>14</sup>R. L. Weiher, J. Appl. Phys. **33**, 2834 (1962).

- <sup>15</sup>P. Ágoston, P. Erhart, A. Klein, and K. Albe, J. Phys.: Condens. Mat. 21, 455801 (2009).

- 16D.-J. Lee, J.-Y. Kwon, J. I. Lee, and K.-B. Kim, J. Phys. Chem. C 115, 15384 (2011).

- <sup>17</sup>A. U. Mane, A. J. Allen, R. K. Kanjolia, and J. W. Elam, J. Phys. Chem. C 120, 9874 (2016).

- <sup>18</sup>O. Bierwagen, J. S. Speck, T. Nagata, T. Chikyow, Y. Yamashita, H. Yoshikawa, and K. Kobayashi, Appl. Phys. Lett. 98, 172101 (2011).

- <sup>19</sup>P. D. C. King, T. D. Veal, F. Fuchs, C. Y. Wang, D. J. Payne, A. Bourlange, H. Zhang, G. R. Bell, V. Cimalla, O. Ambacher, R. G. Egdell, F. Bechstedt, and C. F. McConville, Phys. Rev. B 79, 205211 (2009).